硬件开发者之路,EMC设计从电源,信号,布局,ESD等各方面要点

在电子电路系统设计中EMC对于很多新手来说都快成为“玄学”了,主要原因是说起来简单,处理起来难。 简单说起来就是内外部干扰,处理起来难常常就是一团乱麻找不到问题点。无论是普通电路系统还是高速电路系统,我们对于EMC的处理都很有必要,那么今天来分享一篇文章学习几个要点,实际上遵循这几个原则,可以大大减小EMC出现问题的概率。

一、电源系统处理

一个原则:要有源和阻抗的概念,源需要最大限度达到IC然后由地最快返回。

这是PDN系统的设计划分。

电源抑制比(PSRR)的基础知识 - 电源/新能源 - 电子发烧友网

电源抑制比 ,英文名Power Supply Rejection Ratio,简称PSRR,它描述了电路抑制任何电源变化传递到其输出信号的能力,通常以dB为单位进行测量,用来描述输出信号受电源影响。它最常与运算放大器 (op amps)、DC-DC转换器、线性稳压器和低压差稳压器 (LDO) 的使用相关。

对于运算放大器,电源抑制比描述了放大器在其直流电源电压变化时保持其输出电压的能力。与此同时,电源抑制比量化了在电源转换应用中阻止来自输入源的纹波电压的能力。

电源纹波抑制比(PSRR)是输入电源变化量(以伏为单位)与转换器输出变化量(以伏为单位)的比值,常用分贝表示。对于高质量的D/A转换器,要求开关电路及运算放大器所用的电源电压发生变化时,对输出的电压影响极小。通常把满量程电压变化的百分数与电源电压变化的百分数之比称为电源纹波抑制比。

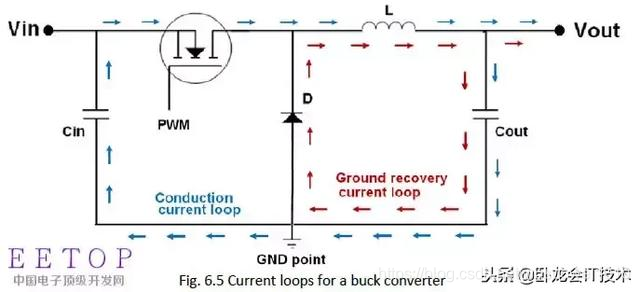

开关电源的设计要点就在于开关电流回路的处理,回路要小!

对于覆铜处理:避免RF部分通过耦合干扰数字GND噪声数字电路异常,注意辐射区的耦合干扰问题。

避免形成大的源环路,进行Plane层的桥接。

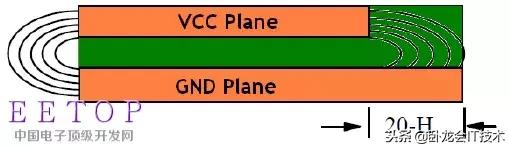

Plane层的覆铜注意在边缘留间隙,减小边缘效应的影响。

去耦电容就近放置,减小寄生电感,避免去耦失效。

注意交流路径和直流路径的区别在于耦合。

关于信号地和支架的接地处理,接地的目的是提供干扰的泄放路径,环路开口的目的是避免形成大环路天线,造成EMI干扰。

二、信号的考虑

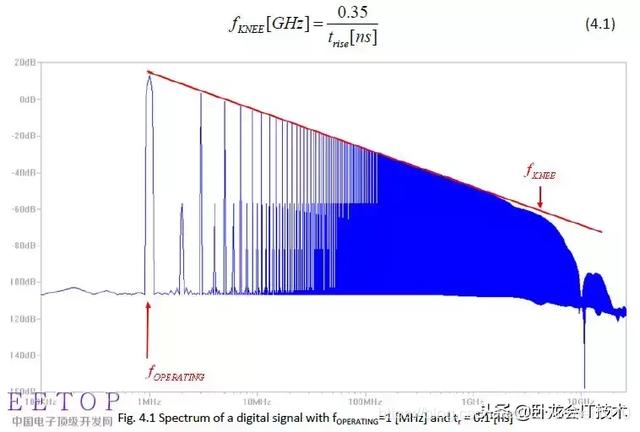

高速信号的频谱如上图,我们的目的是把所有的能量都传输到接收端。

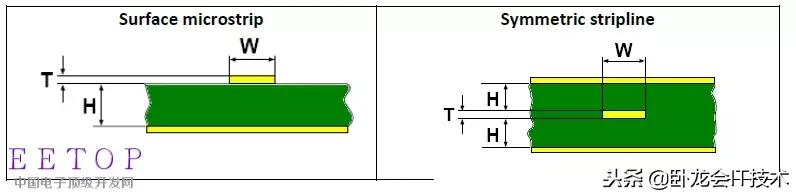

传输线的阻抗等效:

微带线的模型:

差分信号的耦合模型:

传输线的阻抗:

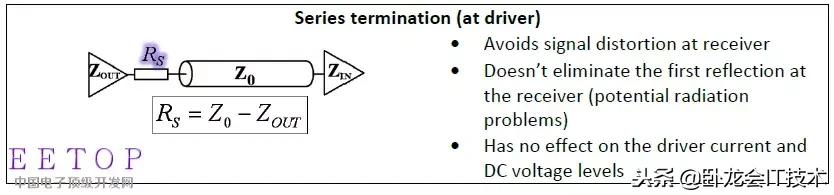

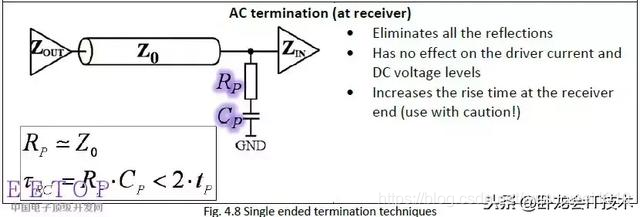

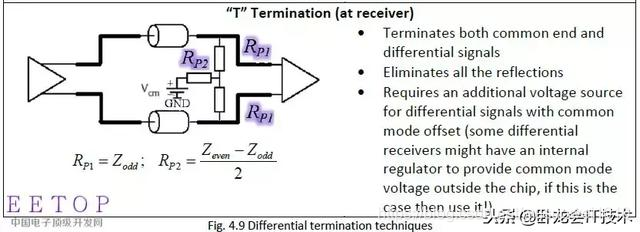

几种端接匹配:

三、布局

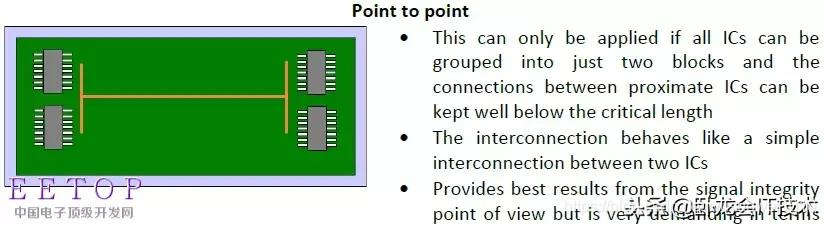

连线:

连线的原则就是本着最短距离和最小阻抗以减小过程干扰。

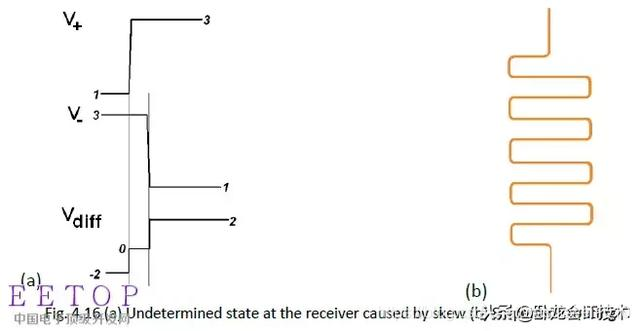

眼图形成的原因是一系列数字信号的叠加效果,反应的是传输信号质量。

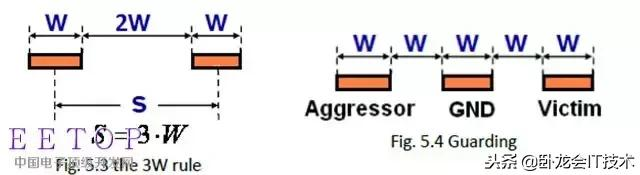

简单的3W原则。

晶振的布线特殊注意:

四、ESD问题

ESD问题非常常见,是造成芯片损坏的重要原因,尤其是在生产过程中,TVS是**防护器件。

小结:这里只是一篇简单的EMC设计说明文章,我觉得最重要的地方还是上面说的环路概念,对于普通应用而言处理好电源系统的设计基本就没有问题了,但是对于高速电路系统参照一些基本简单的原则也会减小出问题的概率,而且EMC设计需要充分的理解设计原理然后在实际中反复测试和验证,技无高低,唯手熟尔。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/50839.html