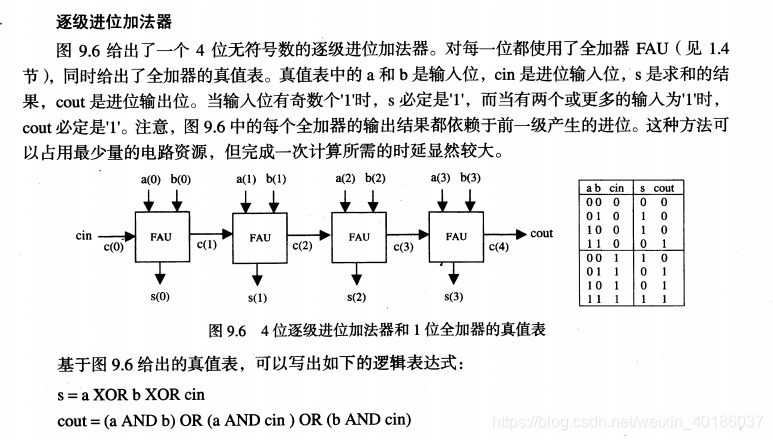

关于逐级进位加法器:

讯享网

VHDL实现:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity adder_cripple is generic(n:integer:=4); port( a,b:in std_logic_vector(n-1 downto 0); cin: in std_logic; s:out std_logic_vector(n-1 downto 0); cout: out std_logic ); end adder_cripple; architecture Behavioral of adder_cripple is signal c:std_logic_vector(n downto 0); begin c(0)<= cin; --这里的c是信号 G1: for i in 0 to n-1 generate s(i)<= a(i) xor b(i) xor c(i); c(i+1) <= (a(i) and b(i)) or (a(i) and c(i)) or (b(i) and c(i)); end generate; cout <= c(n); end Behavioral; 讯享网

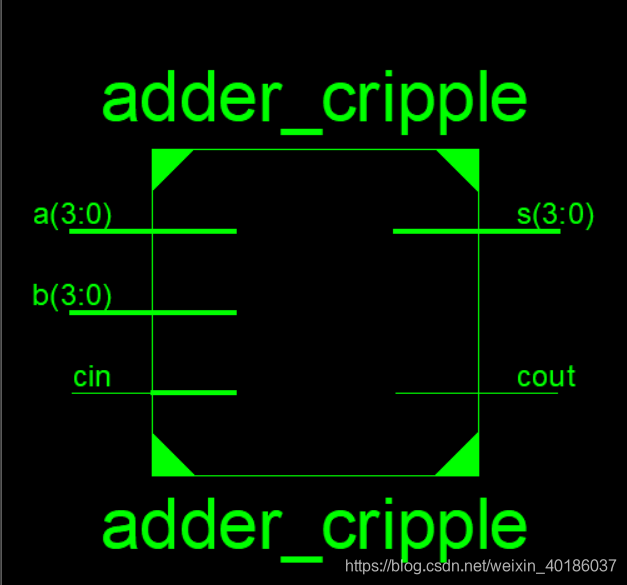

原理图:

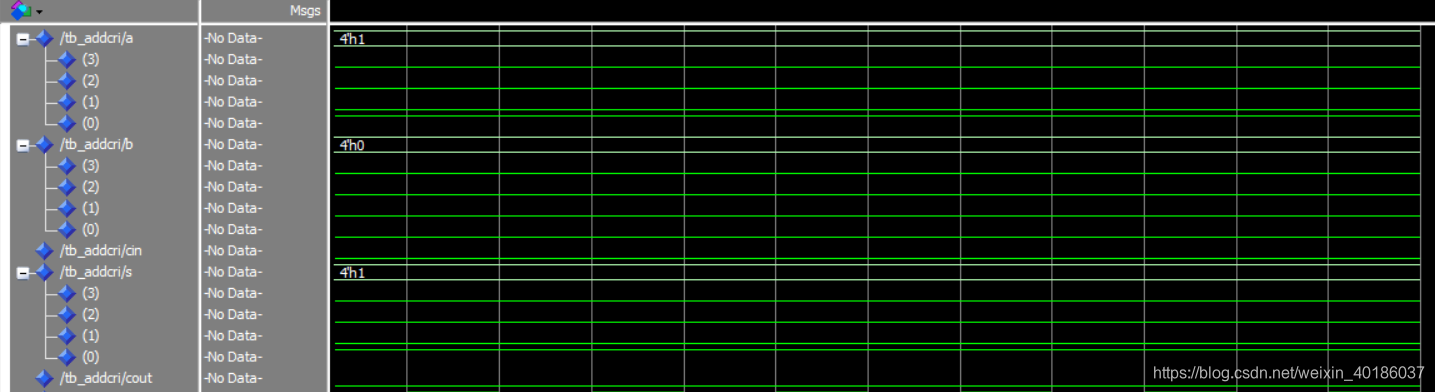

进行测试:

讯享网LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY tb_addcri IS END tb_addcri; ARCHITECTURE behavior OF tb_addcri IS COMPONENT adder_cripple PORT( a : IN std_logic_vector(3 downto 0); b : IN std_logic_vector(3 downto 0); cin : IN std_logic; s : OUT std_logic_vector(3 downto 0); cout : OUT std_logic ); END COMPONENT; --Inputs ---signal a : std_logic_vector(3 downto 0) := (others => '0'); ---signal b : std_logic_vector(3 downto 0) := (others => '0'); signal a : std_logic_vector(3 downto 0) := "0001"; signal b : std_logic_vector(3 downto 0) := "0000"; signal cin : std_logic := '0'; --Outputs signal s : std_logic_vector(3 downto 0); signal cout : std_logic; signal clk,rst:std_logic; constant clk_period : time := 10 ns; BEGIN -- Instantiate the Unit Under Test (UUT) uut: adder_cripple PORT MAP ( a => a, b => b, cin => cin, s => s, cout => cout ); clk_process :process begin clk <= '0'; wait for clk_period/2; clk <= '1'; wait for clk_period/2; end process; stim_proc: process begin rst<='0'; wait for 10 ns; rst<='1'; wait; end process; END;

modelsim仿真:

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/29179.html