目录

前言

一、整体电路结构介绍

二、74LS161介绍

三、分频电路实现

3.1相关知识

3.2 74ls161仿真实现

3.2.1 4位二进制计数基本功能演示

3.2.2 预置数实现分频

3.2.3 清零实现分频

3.2.3 级联实现50%占空比分频

3.2.4 分频总结

四、cd4046介绍

五、锁相环实现

前言

本篇文章主要是记录使用cd4046锁相环与74ls161构成倍频电路。

一、整体电路结构介绍

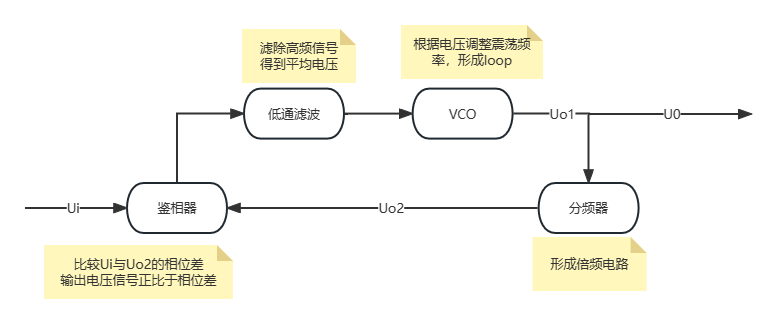

众所周知,锁相环(PLL)的实现一般包括压控振荡器(VCO)、分频器、鉴相器、低通滤波器和压控震荡器构成的环路而成。结构如下:

其中分频器分频倍数决定了锁相环最终产生的信号频率,即N倍频需要分频器进行N分频。

接下来我们逐步实现倍频。

二、74LS161介绍

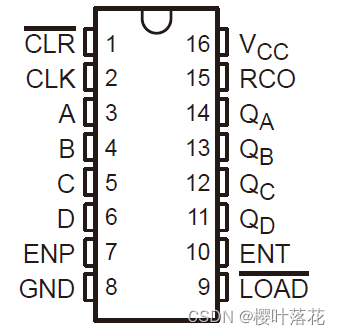

首先进行分频电路的实现,我们选择74ls161。

了解芯片先从datasheet开始!进入芯片官网下载datasheet,对于74ls161,可以进入TI官网搜索,这里放上文档直链。

TOP VIEW

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/16574.html