目录

前言

OPPOSITIE_EDGE模式

SAME_EDGE模式

SAME_EDGE_PIPELINED模式

总结

前言

7系列设备在ILOGIC块中具有专用寄存器,用于实现输入双倍数据速率(DDR)寄存器。此功能用于实例化IDDR基元。

输入I/O tile的所有时钟都是完全多路复用的,即在ILOGIC和OLOGIC区块之间没有时钟共享。IDDR原语支持以下操作模式:

•OPPOSITIE_EDGE模式

•SAME_EDGE模式

•SAME_EDGE_PIPELINED模式

SAME_EDGE和SAME_EDGE_PIPELINED模式与Virtex-6相同

这些模式允许设计者通过ILOGIC块中的域将下降沿数据传输到上升沿,这样可以节省CLB和时钟资源并增加性能(performance在此处应该翻译为“性能”)。

这些模式是使用DDR_CLK_EDGE属性实现的。以下各节详细介绍了每种模式。

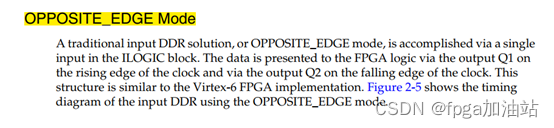

OPPOSITIE_EDGE模式

传统的输入DDR解决方案或OPPOSITIE_EDGE模式是通过单个ILOGIC块中的输入来实现的。数据在时钟的上升沿通过引脚Q1输出给FPGA逻辑,在时钟的下降沿通过Q2输出给FPGA逻辑。这结构类似于Virtex-6的FPGA实现。图2-5显示了使用OPPOSITIE_EDGE模式的输入DDR时序图。

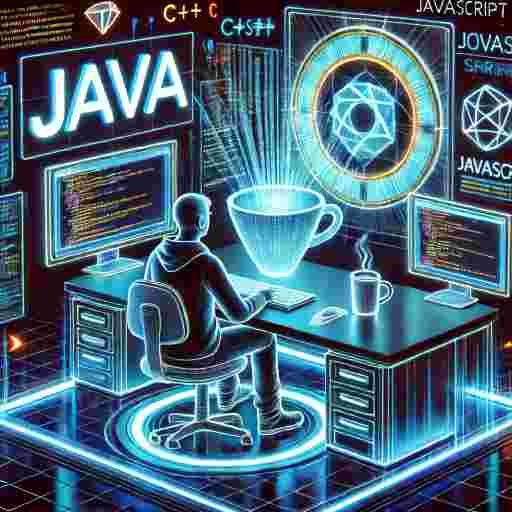

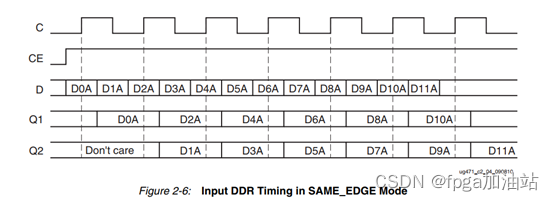

SAME_EDGE模式

在SAME_EDGE模式中,数据在同一时钟沿上呈现到FPGA逻辑中。这种结构类似于Virtex-6的FPGA实现。

图2-6显示了使用SAME_EDGE模式的输入DDR的时序图。可以看到,从Q1和Q2引脚输出的第一对数据不再是Q1(D0A)和Q2(D1A)。相反,第一对呈现的是Q1(D0A)和Q2(Don’t care),紧接着的下一对数据是Q1(D2A)和Q2(D1A)。

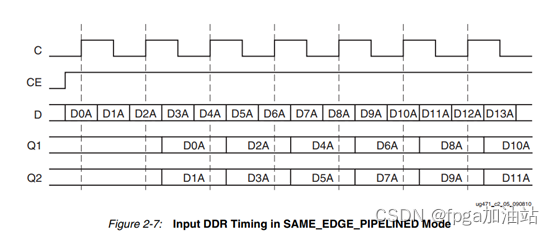

SAME_EDGE_PIPELINED模式

在SAME_EDGE_PIPELINED模式中,数据在同一时钟沿上呈现到FPGA逻辑中。与SAME_EDGE模式不同,数据对不被一个时钟周期分隔。然而需要额外的时钟延迟来消除SAME_EDGE模式的分离效应。图2-7显示了使用SAME_EDGE_PIPELINED模式的输入DDR的时序图。输出对Q1和Q2被同时提供给FPGA逻辑。

总结

| OPPOSITIE_EDGE模式 |

在该模式下,上升沿采样到的数据(如D0A)和下降沿采样到的数据(如D1A),可以在下一个时钟周期的上升沿从Q1,Q2端口读取。 |

| SAME_EDGE模式 |

在该模式下,上升沿读取的数据,可以在下一个时钟周期的上升沿从Q1端口读取,而下降沿读取的数据,可以在下下个时钟周期的上升沿从Q2端口读取。 |

| SAME_EDGE_PIPELINED模式 |

在该模式下,上升沿和下降沿捕获的数据将可以在下下个时钟周期的上升沿从Q1,Q2端口读取。 |

以上便是对Xilinx源语IDDR的一个简单介绍,后续更多关于IDDR的内容将会发布在公众号“fpga加油站”。欢迎大家关注阅读。同时,公众号还为大家提供了大量fpga学习资料以及Xilinx中文文档。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/125017.html