一、PCIE简介

PCI Express (peripheral component interconnect express) 简称PCIe,是一种高速、串行、全双工、计算机扩展总线标准,采用高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中两端只能各连接一个设备。相对于PCI引入了一些新特性,如流量控制机制、服务质量管理(QoS)、热插拔支持、数据完整性和新型错误处理机制等。

PCIe 总线在实际工程实践中有着良好的应用,主要应用在光纤、PCIe 数据采集卡、FPGA 加速卡、存储子系统等所有需要和主机进行高速数据交互的场所。

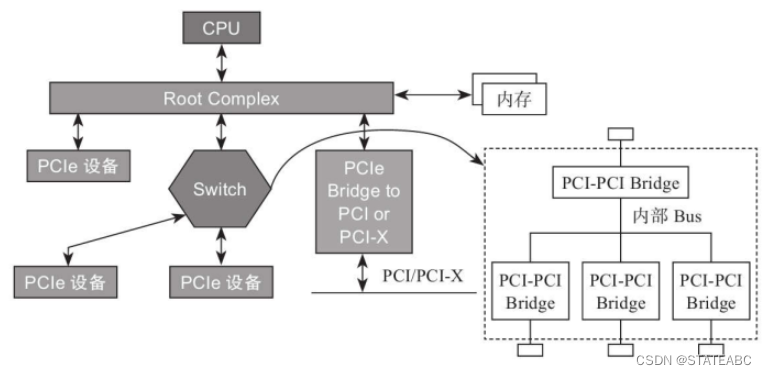

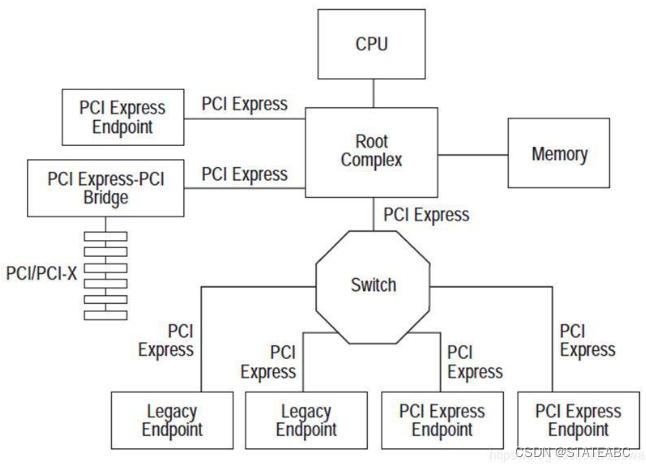

二、PCIE拓扑结构

PCIE是一个协议,描述了具有相同接口的不同设备的沟通方法。PCIe拓扑结构是一个树结构,该拓扑结构的最大特点就是点对点互联,层次结构的顶层是一个CPU,一般包含一根组件RC(Root Complex),交换器switch,终端设备EP(endpoint)等类型的PCIE设备组成。它们在PCIE所规定的协议下扮演着各自的角色,承担着各自的任务。

2.1 Root Complex

Root Complex:根复合体,简称RC,CPU和PCle总线之间的接口,代表CPU与系统的其余部分进行通信,可以理解为系统CPU和PCle拓扑之间的接口,主要功能是完成存储器域到PCIe总线域的地址转换,RC把来自CPU的request转化成PCIe的4种不同的requests(configuration, Memory, I/O, Message)并发送给接在它下面的设备。

简单来说RC是CPU与PCIE上组件各个通信的媒介,比如CPU要读取某个组件信息,告知RC,剩下的任务均由RC进行处理,负责初始化和管理 PCIe 总线上的所有设备,也可以理解为PCIE总线的主控制器。

2.2 PCIE-PCI Bridge

PCIE-PCI Bridge提供了与其他总线(如PCI、PCI- x,或另一个PCle总线)的接口,它允许旧的PCI或PCIX卡通过桥接入系统中。

2.3 Switch

PCIE总线采用端到端的连接方式,,因此在每一条PCIe链路中两端只能各连接一个设备, 如果需要挂载更多的PCIe设备,那就需要用到Switch转接器。

Switch内部可以视为多个虚拟的PCI到PCI的桥,实现扩展功能,允许更多的设备连接到一个PCle端口。该组件会根据事务类型将数据送到不同的通道,对数据包没有处理的功能只有转发功能。在软件层面可以看到switch的上行口(upstream port, 靠近RC的那一侧) 和下行口(downstream port)。一般而言,一个switch 只有一个upstream port, 可以有多个downstream port。

2.4 Endpoint

Endpoint是PCIe总线上的终端设备,负责提供各种服务和数据传输功能,也就是RC命令最终要到达的地方。Endpoint只能接受来自上级拓扑的数据包或者向上级拓扑发送数据包。例如声卡、网卡,还有应用到PCIE的些功能设备,均是端点。

Endpoint可分为Lagacy PCIe Endpoint和Native PCIe Endpoint,Lagacy PCIe Endpoint是指那些原本准备设计为PCI-X总线接口的设备,但是却被改为PCIe接口的设备。Native PCIe Endpoint则是标准的PCIe设备。其中,Lagacy PCIe Endpoint可以使用一些在Native PCIe Endpoint禁止使用的操作,如IO Space和Locked Request等。Native PCIe Endpoint则全部通过Memory Map来进行操作,因此,Native PCIe Endpoint也被称为Memory Mapped Devices(MMIO Devices)

三、PCIE分层结构

PCIE总线架构是一种分层协议架构,分为事务层(Transaction Layer)、数据链路层(Data Link Layer) 和物理层(Physical Layer)。这些层中的每一层都分为两部分:一部分处理出站 (要发送的) 信息,另一部分处理入站 (接收的) 信息。

在PCIE结构中使用数据包在设备之间传递信息,数据包在事务层和数据链路层中形成,以将信息从发送设备传送到接收设备。

3.1 事务层

事务层是PCIE协议的对外接口层,用户对数据进行组帧和解析是在事务层进行,事务层产生的数据包称之为事务层数据包(或事务层报文),即Transaction Layer Packets,TLP)。事务层的主要责任是事务层包TLP的组装和拆卸。事务层接收来自PCIe设备核的数据,并将其封装为TLP。TLP用于传达事务,例如读取和写入,以及确定事件的类型。事务层还可以从数据链路层中接收数据报文,然后转发至PCIe设备核。

3.2 数据链路层

数据链路层的主要职责包括链路管理和数据完整性,包括错误检测和错误纠正。数据链路层在传输链路上接受事务层组装的TLP,检查接收到的TLP的完整性。在检测到TLP错误时,数据链路层负责请求重发TLP,直到正确接收信息或确定链路失败为止。数据链路层还生成并使用用于链路管理功能的数据包,称为数据链路层数据包(Data Link Layer Packet,DLLP),DLLP产生于数据链路层,终止于数据链路层,主要实现的功能有流量控制、电源管理、应答机制和虚拟通道。

TLP在经过数据链路层时被加上Sequence Number前缀和CRC后缀,然后发向物理层。

3.3 物理层

物理层负责将从数据链路层接收的信息转换为适当的序列化格式,并以与链路另一端的设备兼容的频率和通道宽度在PCI Express链路上传输该信息。PCIe总线的物理层定义了 LTSSM(Link Training and Status State Machine)状态机,PCIE链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。

PCIE总线使用端到端的连接方式,在一条PCIE链路的两端只能各连接一个设备,这两个设备互为数据发送端和数据接收端。由于 PCIe 是支持全双工通信的,所以发送端和接收端中都含有TX(发送逻辑)和RX(按收逻辑)。在PCIe总线的物理链路的一个数据通路(Lane)中,有两组差分信号,共4根信号线组成。其中发送端的TX与接收端的RX使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX与接收端的TX使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIE链路可以由多个Lane组成。目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即xl、x2、x4、x8、x12、x16和x32宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

四、PCIe的事务类型

PCIE协议总共规定了Memory、I/O、Configuration和Message四种事务类型(TLP请求),其中前三种是从PCI继承过来的,消息是PCIE所扩展的。前三种分别用于访问内存空间、IO空间、配置空间,Message用于传输中断信息、错误信息等。这四种TLP请求,如果需要对方回应(对方返回一个Completion TLP),称之为Non-Posted TLP;不需要对方回应,称之为Posted TLP。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/57042.html