目录

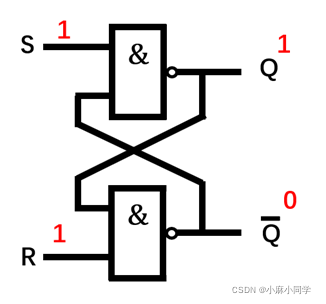

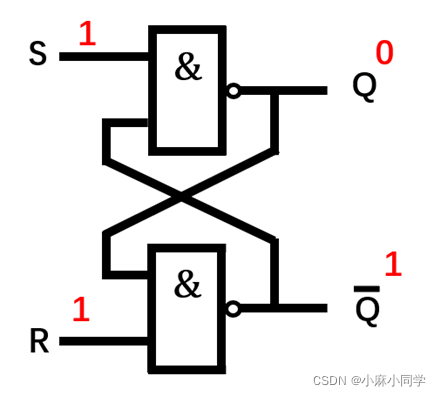

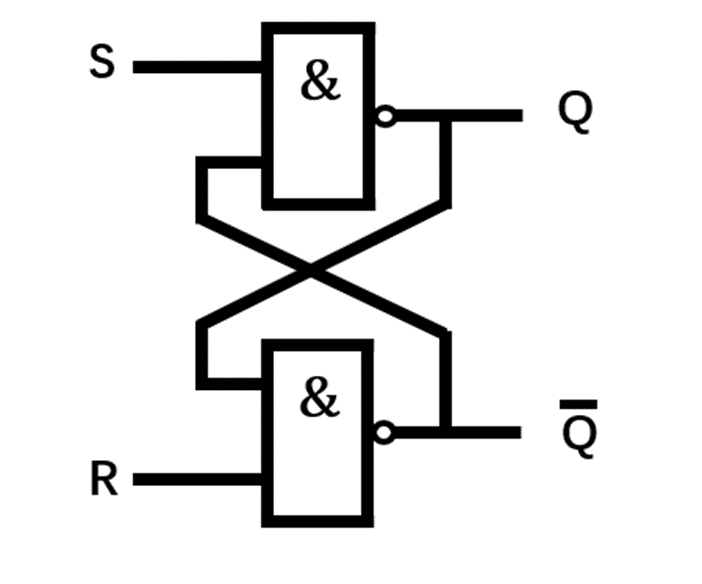

基本RS触发器(与非门构成)如下图所示:

基本含义:

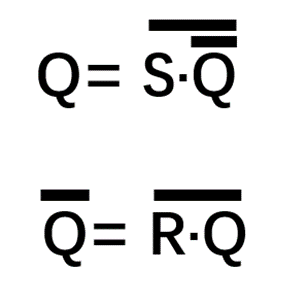

R、S触发器逻辑表达式:

真值表、特征表:

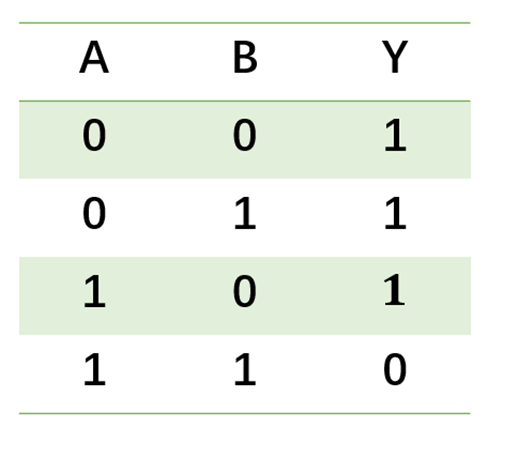

1.与非门真值表:

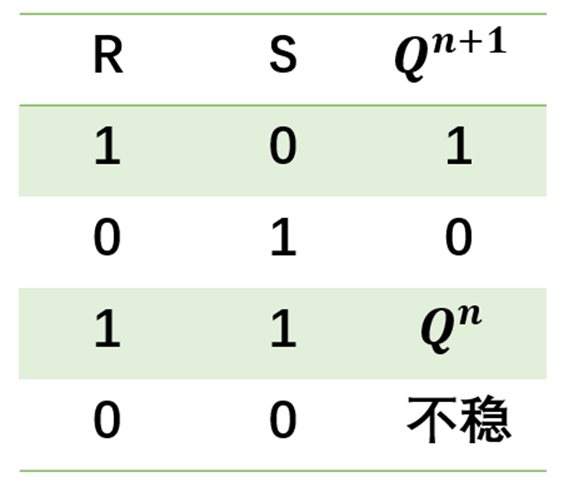

2.基本RS触发器特征表:

特征表含义:

那么为什么R、S都为0时输出不稳定?

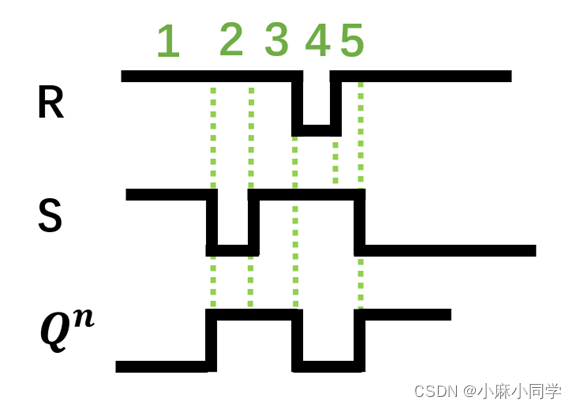

时序图分析理解:

状态1:

状态2:

状态3:

状态4:

状态5:

基本RS触发器1.pdf那么为什么R、S都为0时输出不稳定?-嵌入式文档类资源-CSDN文库

基本RS触发器解析PDF:基本RS触发器解析PDF

晶体管级数字电路设计专栏目录

基本RS触发器(与非门构成)如下图所示:

基本含义:

S是Set 的首字母,也就是设置端。

R 是Reset 的首字母,也就是复位端。

触发器属于时序逻辑电路,与组合逻辑电路不同,组合逻辑电路的输出状态只取决于同时刻的输入信号状态。基本RS触发器把输出信号引回到输入信号,形成一个反馈。这样使得输出信号的状态不但取决于同时刻输入信号的状态,也与输出之前的状态有关。

输出信号的状态就是(Q^(N+1) 次态) 同时刻输入信号的状态就是(S、R) 输出之前的状态就是(Q^N 现态)

R、S触发器逻辑表达式:

真值表、特征表:

1.与非门真值表:

2.基本RS触发器特征表:

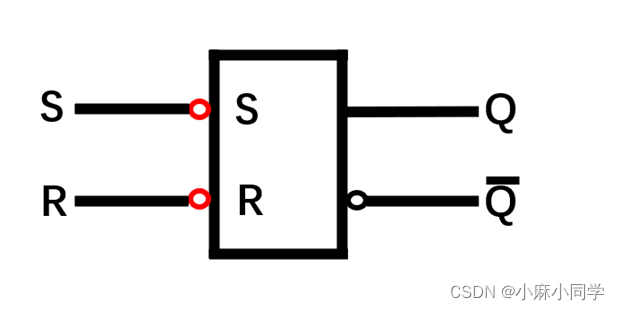

把上图RS触发器包装起来就是:

红色的圈表示R、S均为输入低电平有效。

特征表含义:

第一行:

R是复位端,低电平有效,也就是当R为0时有效,当S为1(设置端无效)时,使得输出Q^(N+1)为0。

第二行:

S是设置端,低电平有效,也就是当S为0时有效,当R为1(复位端无效)时,使得输出Q^(N+1)为1。

第三行:

输入R、S都为1,也就是复位端、设置端都无效。输出保持,为Q^N。

证明:

先假设QN=1,那么QN 非就等于0:

第一个与非门输入 1和0,根据与非门真值表可知,Q^(N+1)输出为1。

第二个与非门输入1和1,根据与非门真值表可知,Q^(N+1) 非输出为0。

Q(N+1)=QN,输出保持不变。

再假设QN=0,那么QN 非就等于1:

第一个与非门输入 1和1,根据与非门真值表可知,Q^(N+1)输出为0。

第二个与非门输入0和1,根据与非门真值表可知,Q^(N+1) 非输出为1。

Q(N+1)=QN,输出保持不变。

综合两次假设:当输入R、S都为1时,输出保持不变。

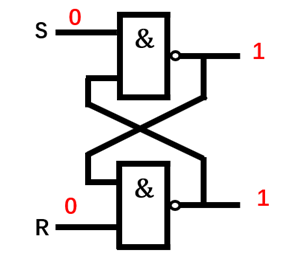

第四行:

当R、S都输入为0时,

根据与非门的特性,两个输出端都为1。

但是当R、S端的下一个信号进入触发器时,其输出状态是不确定的。因此,运用触发器时要尽量避免此状态。

时序图分析理解:

状态1:

R、S输入均为1,输出保持不变仍然为0

状态2:

R输入为1,S输入为0,输出置1

状态3:

R、S输入均为1,输出保持不变仍然为1

状态4:

R输入为0,S输入为1,输出置0

状态5:

R输入为1,S输入为0,输出置1

晶体管级数字电路设计专栏目录

点我回到目录

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/42285.html