关注、星标公众号,精彩内容每日送达讯享网

本文作者:AMD 赛灵思工程师 Hong Han

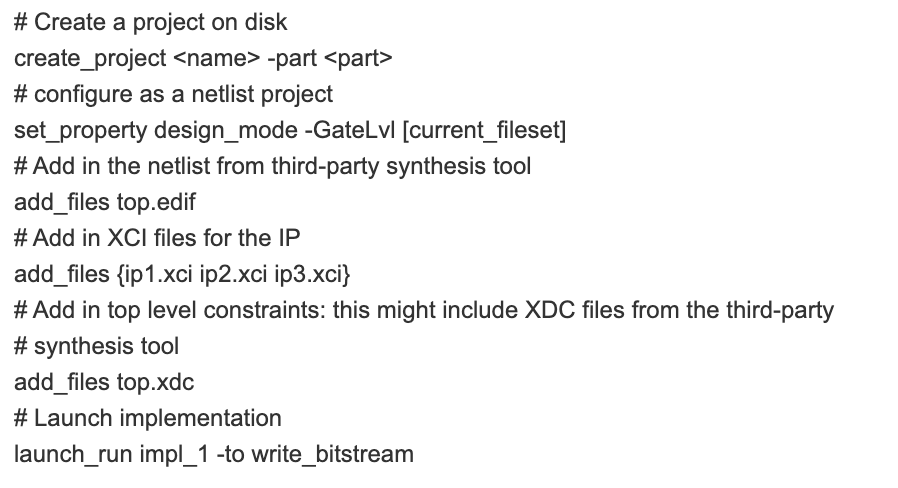

当使用第三方综合器比如 Synopsys® Synplify Pro 或 Mentor® Graphics Precision 来综合包含 AMD Xilinx IP 的设计时,UG896 推荐的方式是创建并定制 IP,生成这些 IP 的 output product (包括 IP 的 dcp);然后把第三方生成的网表文件和 IP XCI 的相关文件都加到 Vivado 的 post-synthesis 工程中。

此时第三方综合器只是综合用户的 RTL 代码,IP 代码的综合实际还是由 Vivado 完成,然后在新的 Vivado 工程中把这些 IP 的网表和第三方综合器生成的顶层网表合并(在 Vivado 中的 link_design 步骤实现)。

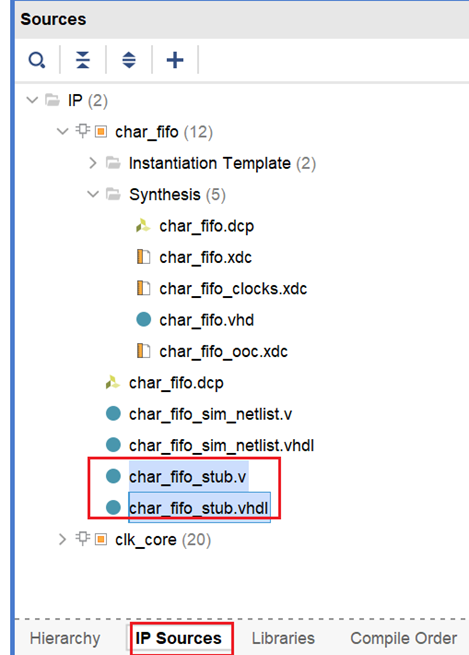

第三方综合器由于并不实际综合 IP 的代码,在第三方综合器综合的过程中,只需要提供 IP 的黑盒文件,让第三方综合器了解 IP 模块的接口即可,生成 IP output product 时得到的 stub 文件就是黑盒文件(_stub.v /_stub.vhdl)。

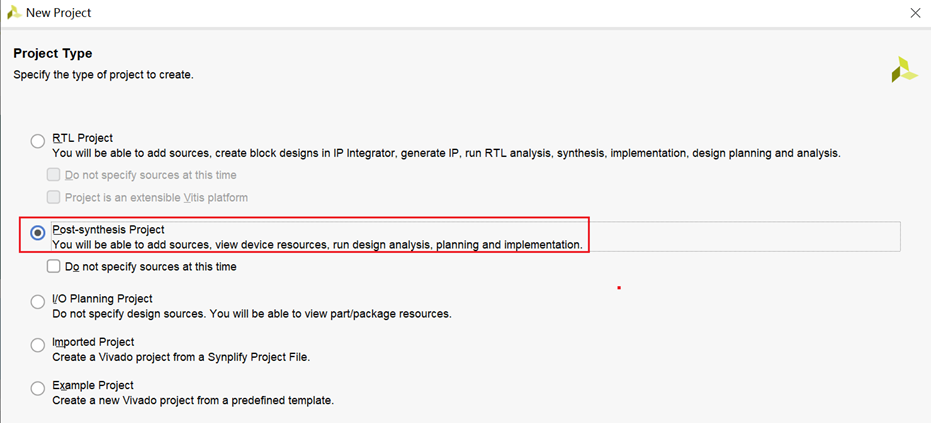

以下是在 GUI 下创建 Post-synthesis 工程的界面:

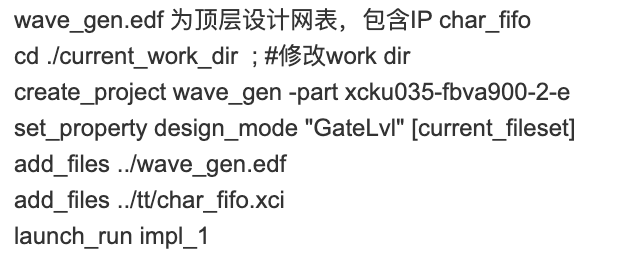

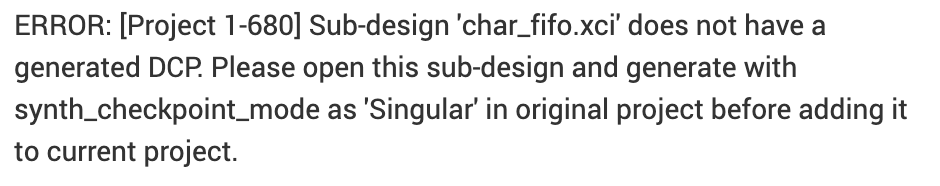

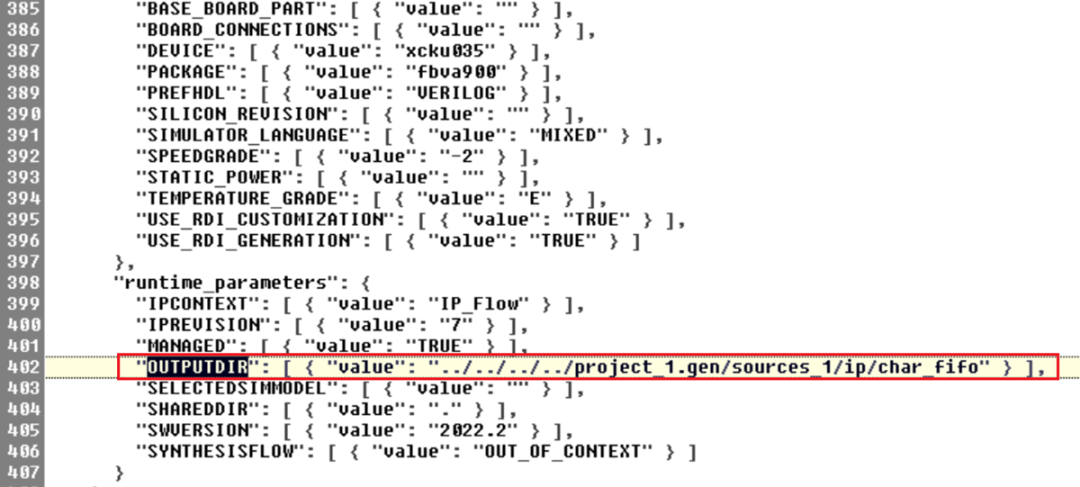

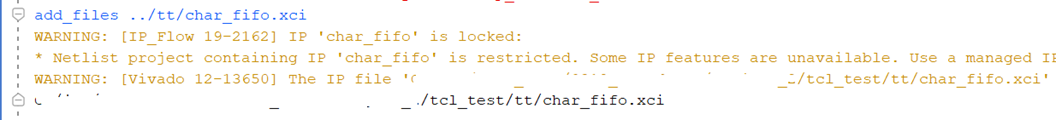

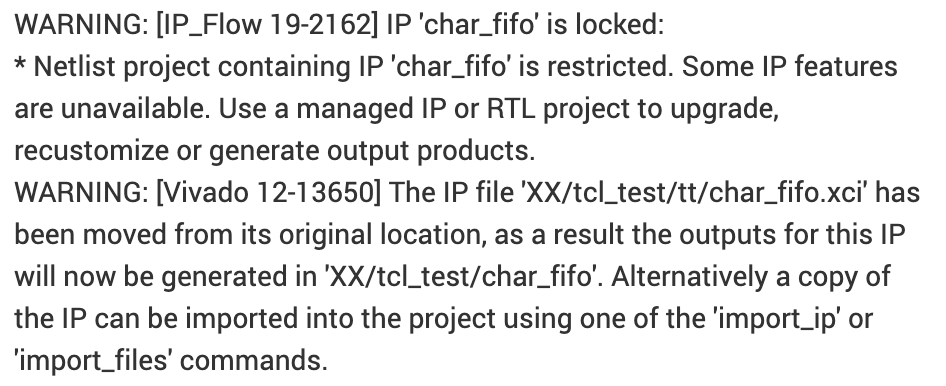

结果 IP char_fifo 没能加到新的工程中,并报出以下的错误:

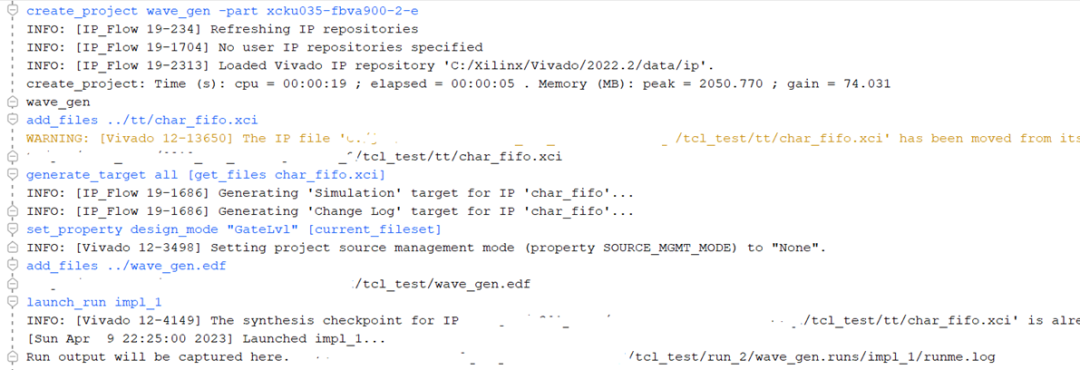

在 Vivado TCL CONSOLE 中重新运行一下加 XCI 文件的命令,可以看到以下输出:

这里可以看到 XCI 文件已经加到工程中,同时看到的 warning 是正常的,提醒用户在 post-synthesis 工程中,IP 是锁定的,无法修改。

在一些早期的 Vivado 版本中(Vivado 2022.2没有这个问题),即使 IP XCI 文件中 OUTPUTDIR 所指向的目录的确是 IP output product 存放的目录,依然会报 ERROR: [Project 1-680]。这里给大家介绍一下如何微调脚本解决这个问题。

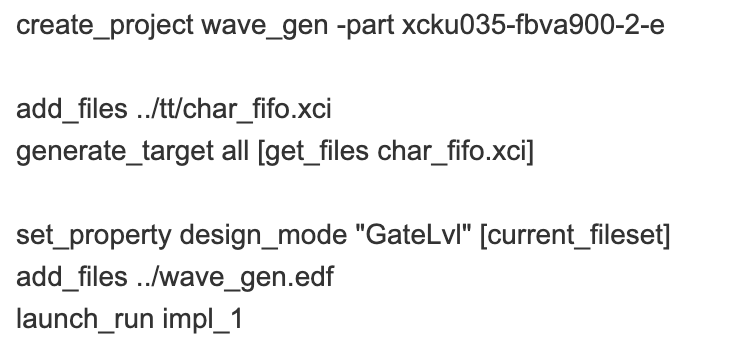

新的脚本:

这里差异在于在新工程设置为 post-synthesis 工程之前,先读入 XCI 文件并重新生成 IP 的 output product。这样就不必修改 XCI 文件的 OUTPUTDIR 去指向之前 output product 的目录。

使用 tcl 命令生成的工程文件 .xpr 文件可以在 Vivado 界面直接打开(File -> Project -> Open)。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/20418.html