如果大家对节点与节点之间无线通信的具体实现与代码有需求的话,可以前往笔者的主页,参考另一篇文章_(实验篇,含所有代码)(因为合在一起太长了,所以分成两篇,也更有目的性一些😁😁)

CC2420电路介绍

简介

CC2420是Chipcon As公司推出的首款符合2.4GHz IEEE802.15.4标准的射频收发器。该器件包括众多额外功能,是第一款适用于ZigBee产品的RF器件。它基于Chipcon公司的SmartRF 03技术,以0.18um CMOS工艺制成,只需极少外部元器件,性能稳定且功耗极低。CC2420的选择性和敏感性指数超过了IEEE802.15.4标准的要求,可确保短距离通信的有效性和可靠性。利用此芯片开发的无线通信设备支持数据传输率高达250kbps,可以实现多点对多点的快速组网。

主要性能参数

CC2420的主要性能参数如下:

1.工作频带范围:2.400~2.4835GHz;

2.采用IEEE802.15.4规范要求的直接序列扩频方式;

3.数据速率达250kbps码片速率达2MChip/s;

4.采用O-QPSK调制方式;

5.超低电流消耗(RX:19.7mA,TX:17.4mA)高接收灵敏度(-99dBm);

6.抗邻频道干扰能力强(39dB);

7.内部集成有VCO、LNA、PA以及电源整流器,采用低电压供电(2.1~3.6V);

8.输出功率编程可控;

9.IEEE802.15.4 MAC层硬件可支持自动帧格式生成、同步插入与检测、16bit CRC校验、电源检测、完全自动MAC层安全保护(CTR、CBC-MAC、CCM);

10.与控制微处理器的接口配置容易(4总线SPI接口);

11.采用QLP-48封装,外形尺寸只有7*7mm。

CC2420芯片的内部结构如下图所示。天线接收的射频信号经过低噪声放大器和I/Q下变频处理后,中频信号只有2MHz,此混合I/Q信号经过滤波、放大、AD变换、自动增益控制、数字解调和解扩,最终恢复出传输的正确数据。

芯片结构图

下图是CC2420的芯片结构

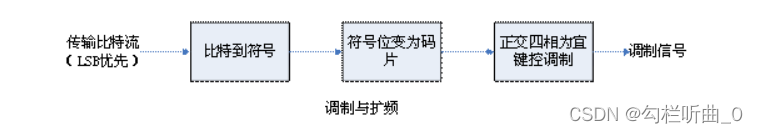

调制和扩频

发射机部分基于直接上变频,要发送的数据先被送入128字节的发送缓存器中,头帧和起始帧是通过硬件自动产生的。根据IEEE802.15.4标准,所要发送的数据流的每4个比特被32码片的扩频序列扩频后送到DA变换器。然后,经过低通滤波和上变频的混频后的射频信号最终被调制到2.4GHz,并经放大后送到天线发射出去。

CC2420调制和扩频的过程如下图。

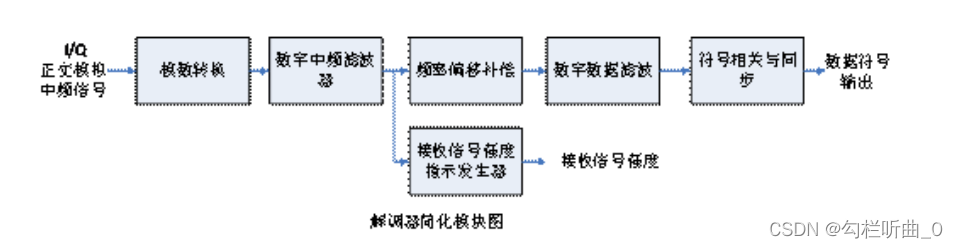

CC2420解调的过程如图

CC2420典型电路

CC2420只需要极少的外围元器件,其典型应用电路如下图所示。它的外围电路包括晶振时钟电路、射频输入/输出匹配电路和微控制器接口电路三个部分。CC2420可以通过4线SPI总线(SI、SO、SCLK、CSN)设置芯片的工作模式,并实现读/写缓存数据读/写状态寄存器等,通过控制FIFO和FIFOP管脚接口的状态可设置发射/接收缓存器。注意:在SPI总线接口上进行的地址和数据传输大多是MSB优先的。CC2420片内有33个16比特状态设置寄存器,在每个寄存器的读/写周期中,SI总线上共有24比特数据,分别为:1比特RAM/寄存器选择位(0:寄存器,1:RAM),1比特读/写控制位(0:写,1:读),6比特地址选择位、16比特数据位。在数据传输过程中CSN必须始终保持低电平。

另外,通过CCA管脚状态的设置可以控制清除通道估计,通过SFD管脚状态的设置可以控制时钟/定时信息的输入。这些接口必须与微处理器的相应管脚相连来实现系统射频功能的控制与管理。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/124178.html