第四章 数值的机器运算

1.1 基本算术运算的实现

1.1.1 加法器

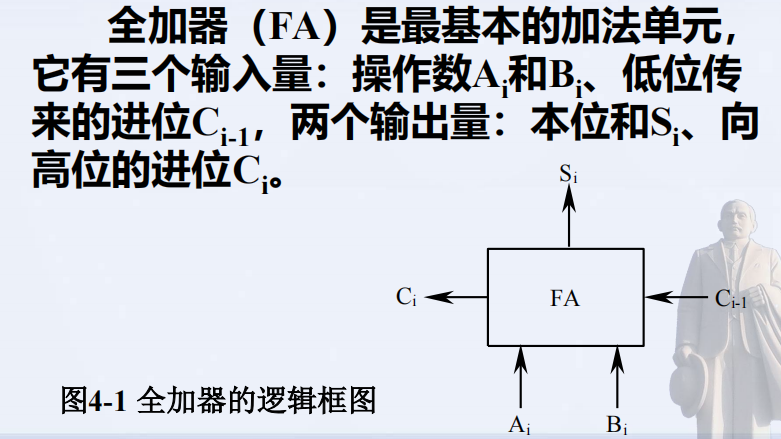

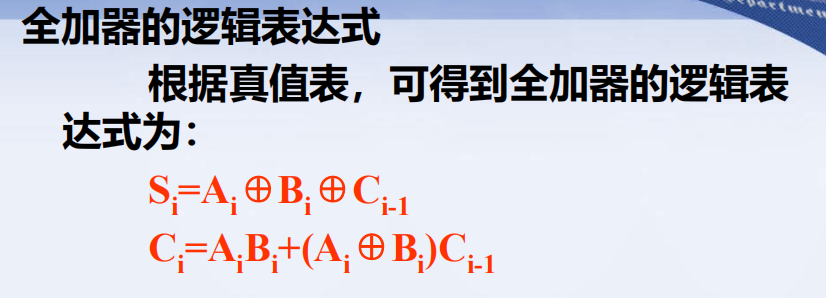

1、全加器

2、串行加法器与并行加法器

(1)加法器有串行和并行之分。在串行加法器中,只有一个全加器。并行加法器则由多个全加器组成。

(2)串行加法器

优点:具有器件少、成本低

缺点:运算速度太慢,低速专用运算器采用并行加法器

(4)最长运算时间

主要由进位信号的传递时间决定,而每个全加器本身的求和延迟只是次要因素。很明显,提高并行加法器速度的关键是尽量加快进位产生和传递的速度。

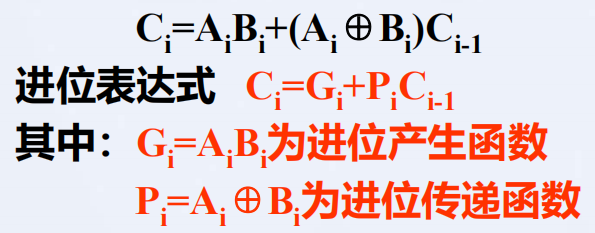

1.1.2 进位的产生和传递

1、进位表达式

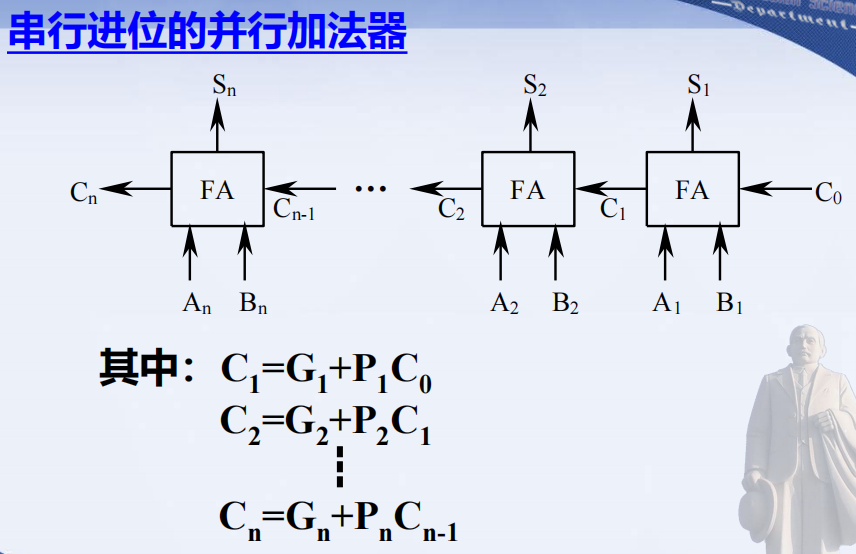

2、串行进位的并行加法器

总延迟时间:与字长成正比。

1、每一级全加器的进位延迟时间为2ty

2、字长=n时,若从C0→Cn的最长延迟时间为2nty

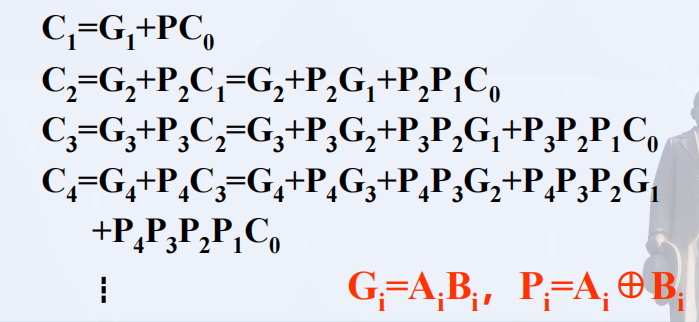

1.3 并行加法器的快速进位

1、并行进位方式

(1)并行进位又叫先行进位、同时进位,其特点是各级进位信号同时形成。

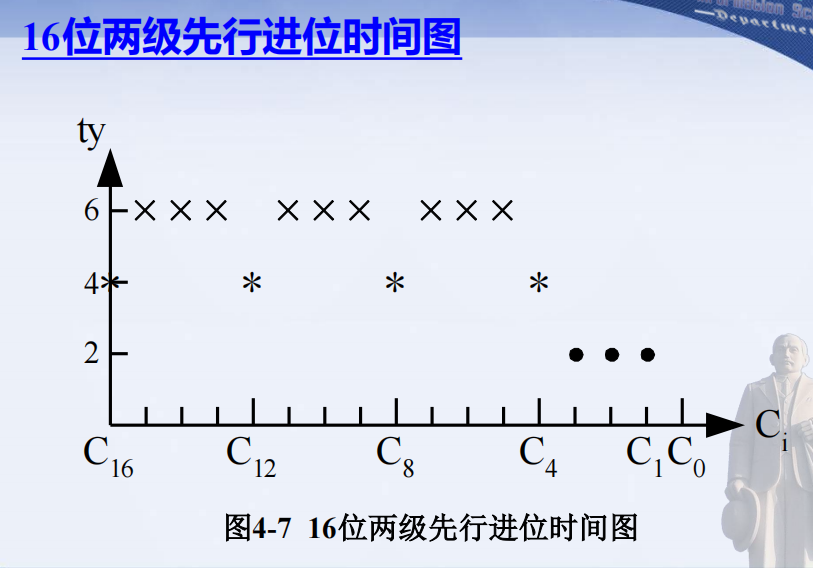

(2)这种进位方式是快速的,若不考虑Gi、Pi的形成时间,从C0→Cn的最长延迟时间仅为2ty,而与字长无关

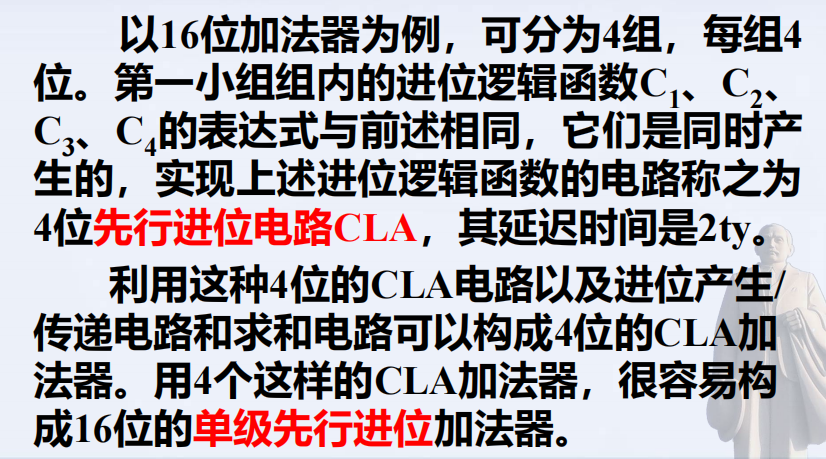

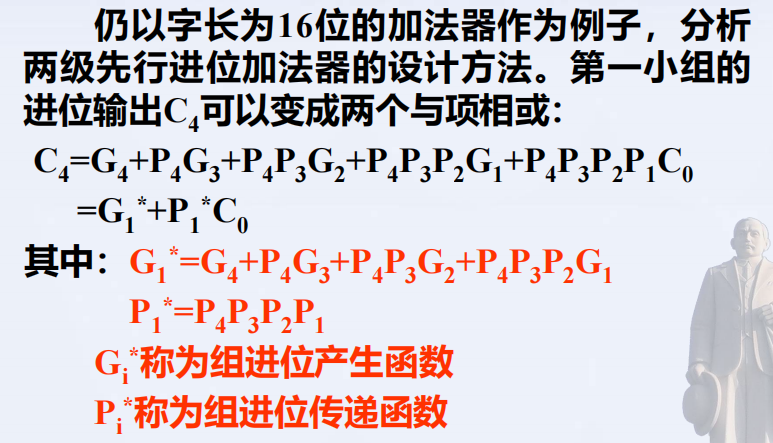

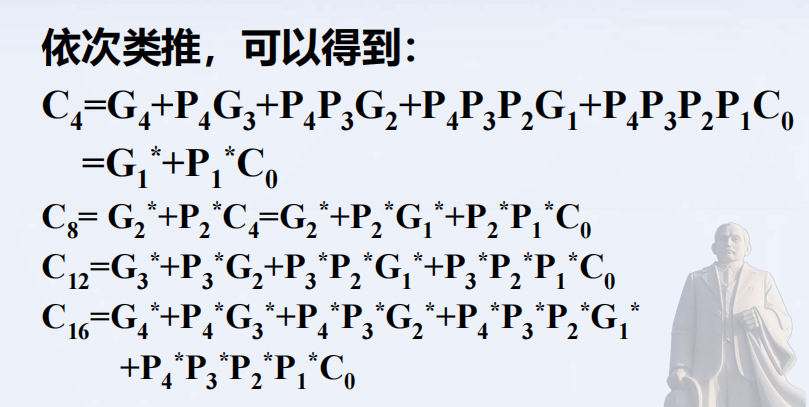

2、分组并行进位方式

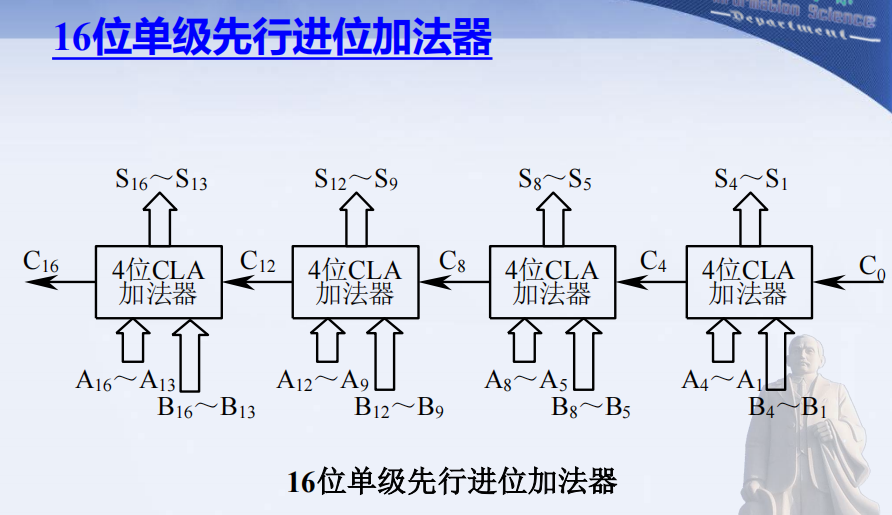

(1)单级先行进位方式(组内并行、组间串行)

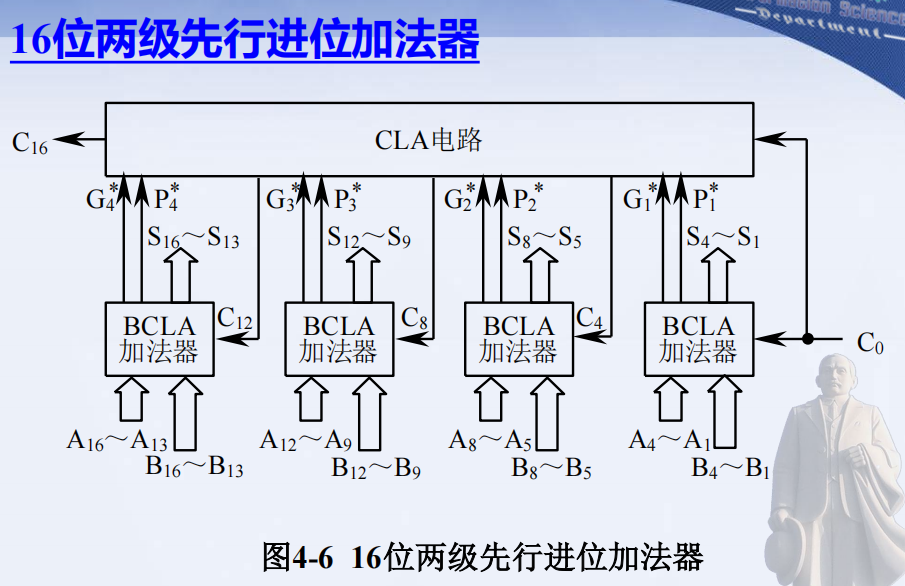

(2)多级先行进位方式(组内并行、组间并行)

1.2 定点加减运算

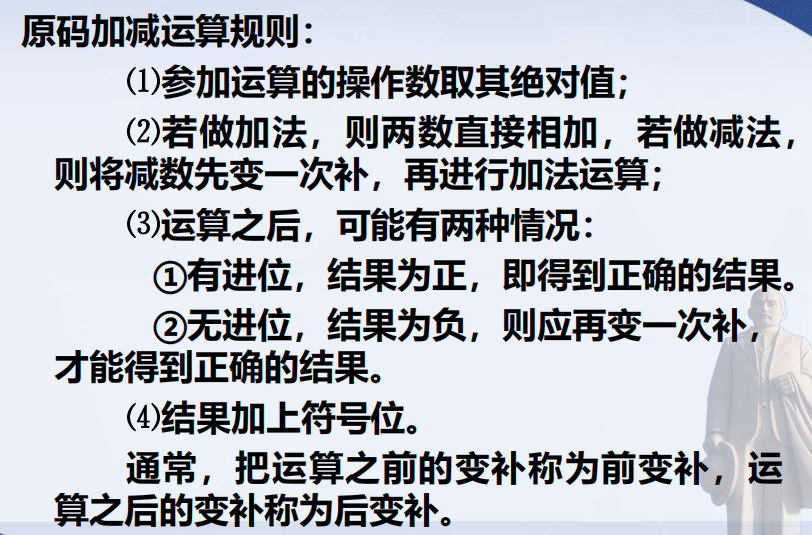

1.2.1 原码加减运算

1.2.2 补码加减运算

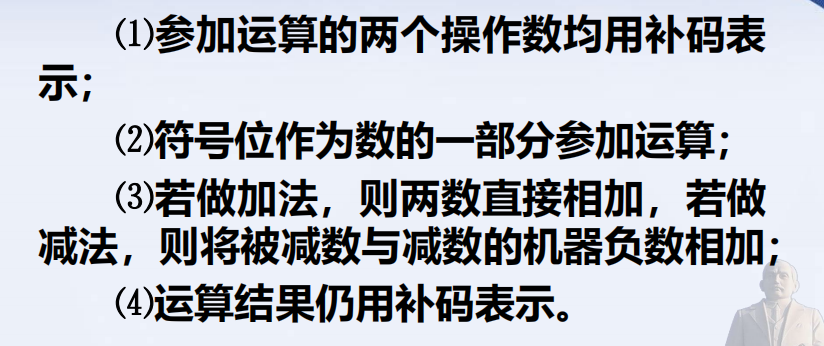

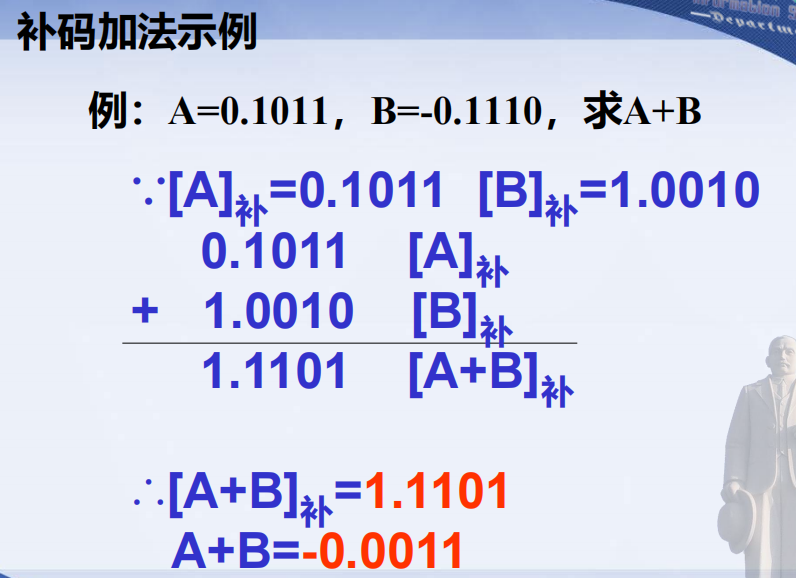

1、补码加法

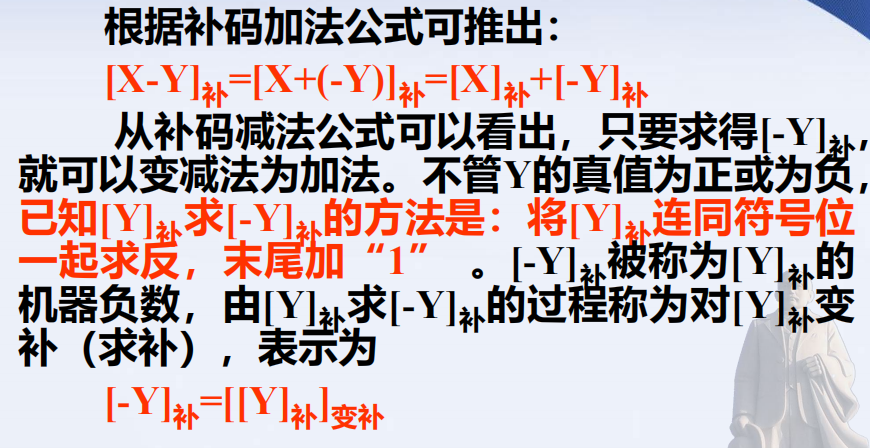

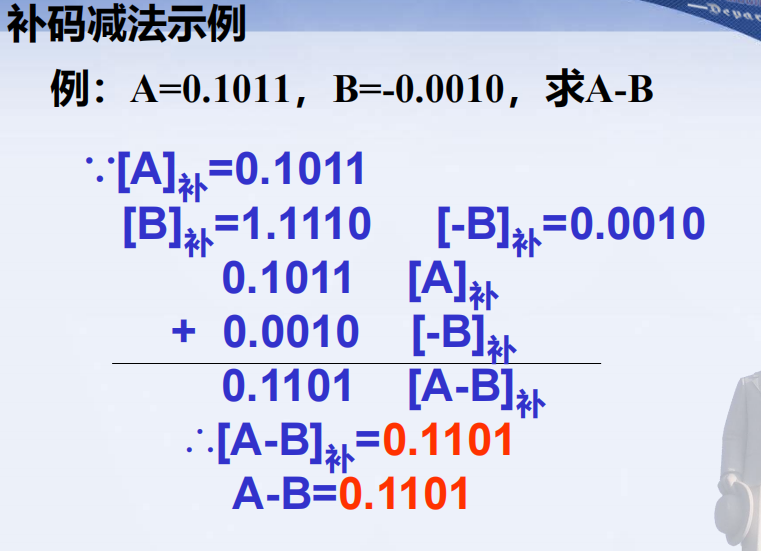

2、补码减法

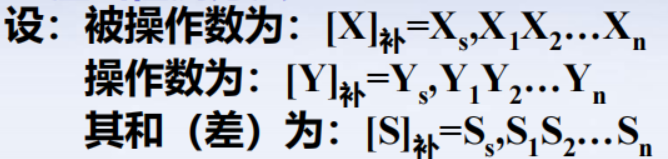

3、补码加减运算规则

4、符号扩展

补码的符号扩展非常简单,所有附加位均用符号位填充,即正数用0进行填充,负数用1填充。

1.2.3 补码的溢出判断与检测方法

1、溢出的产生

1)字长为n+1位的定点整数(其中一位为符号位),采用补码表示,当运算结果大于2n-1或小于-2n时,就产生溢出。

2)将两正数相加产生的溢出称为正溢;反之,两负数相加产生的溢出称为负溢

2、溢出检测方法

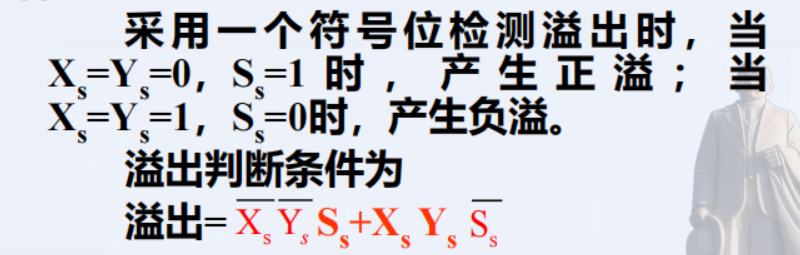

1)采用一个符号位

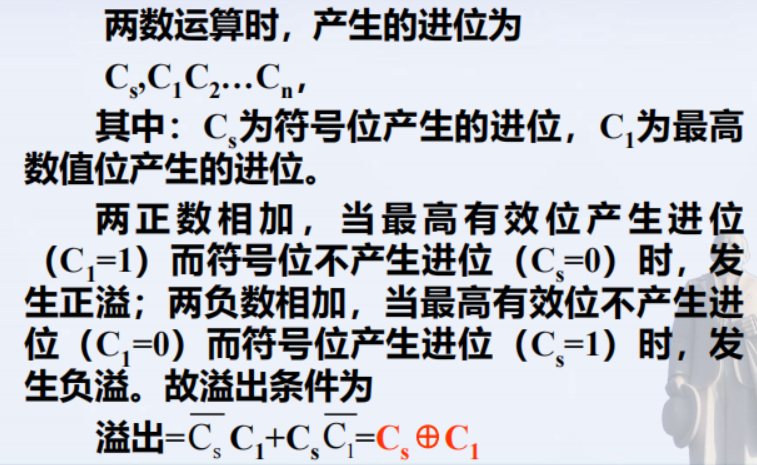

2)采用进位位判断

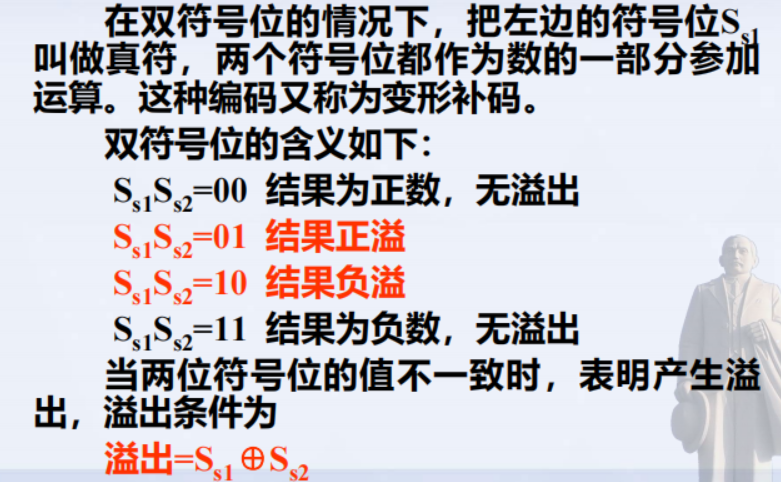

3)采用变形补码(双符号位补码)

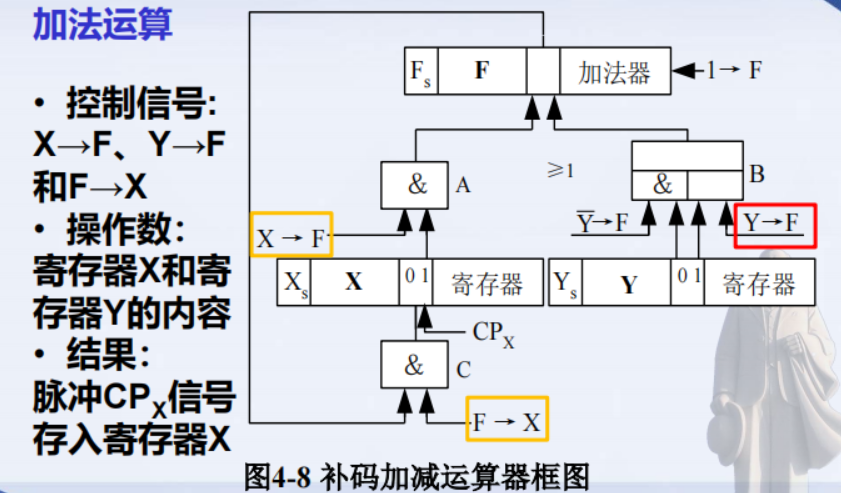

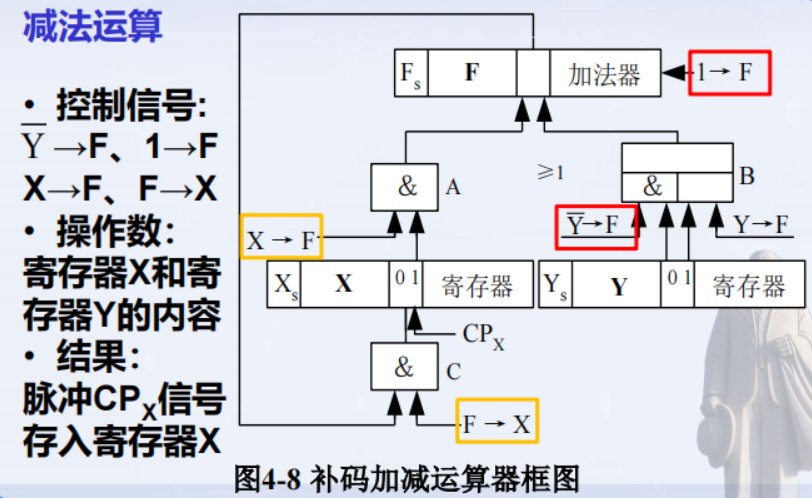

1.2.3 补码定点加减运算的实现

1)减法与加法的不同之处在于,加法使用Y→F控制信号,减法使用Y →F 和 1→F控制信号,其余控制信号相同。

2)加法运算

3)减法运算

1.3 带符号数的移位和舍入操作

1.3.1 带符号数的移位操作

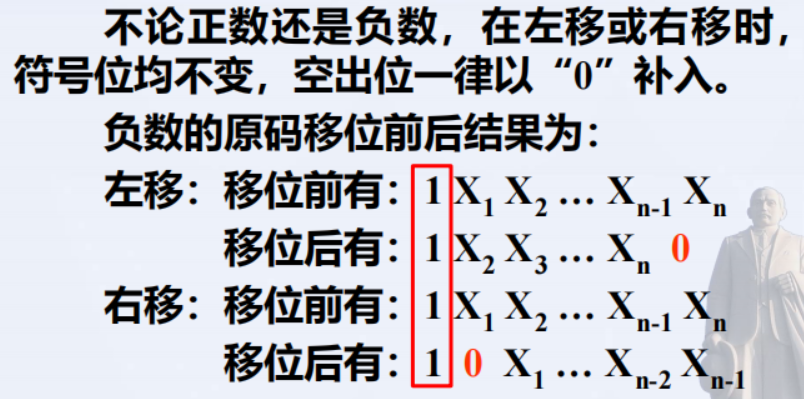

1、原码的移位规则

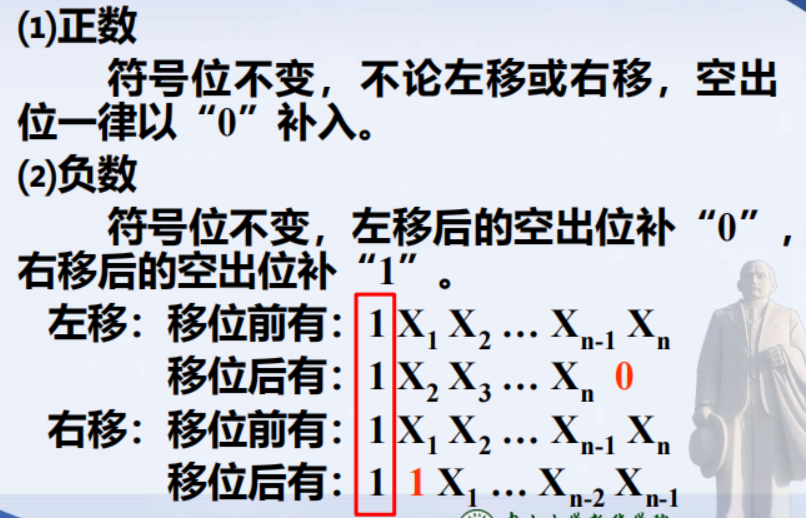

2、补码的移位规则

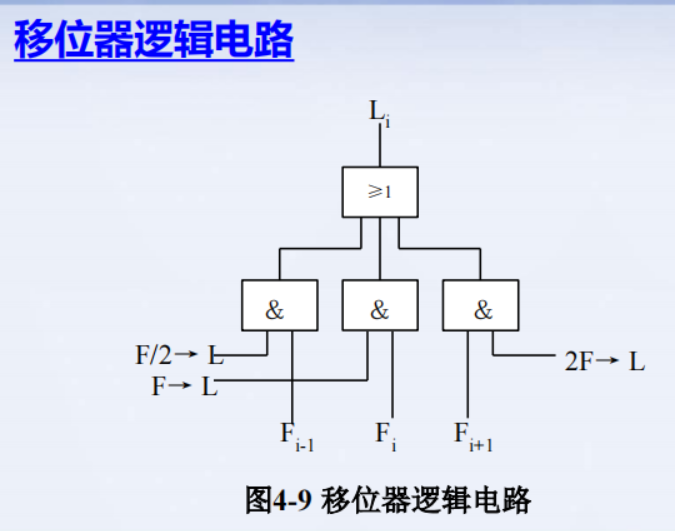

3、移位功能的实现

移位器是由与门和或门组成的逻辑电路(实际是一个多路选择器),可以实现直传(不移位)、左斜一位送(左移一位)和右斜一位送(右移一位)的功能。

1.3.2 带符号数的舍入操作

经过运算后的数共有p+q位,现仅允许保留前p位。常见的舍入方法有:

1)恒舍(切断)

无论多余部分q位为何代码,一律舍去,保留部分的p位不作任何改变。

2)冯·诺依曼舍入法

这种舍入法又称为恒置1法,即不论多余部分q位为何代码,都把保留部分p位的最低位置1。

3)下舍上入法

下舍上入就是0舍1入。用将要舍去的q位的最高位作为判断标志,以决定保留部分是否加1。如该位为0,则舍去整个q位 (相当于恒舍);如该位为1,则在保留的p位的最低位上加1。

1.4 定点乘法运算

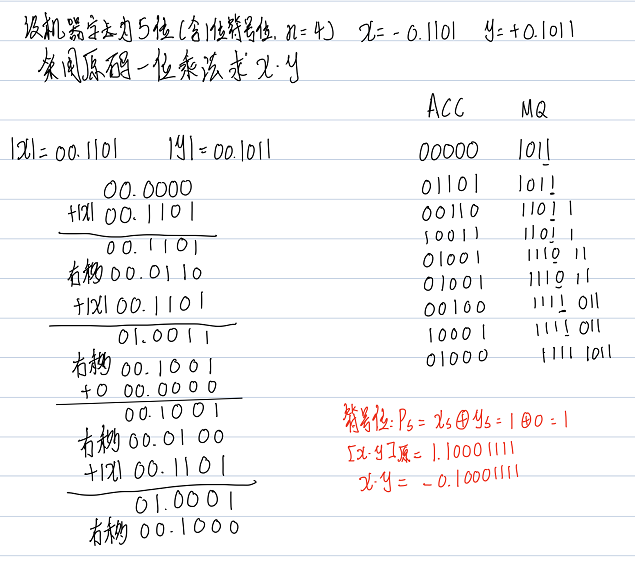

1.4.1 原码一位乘法

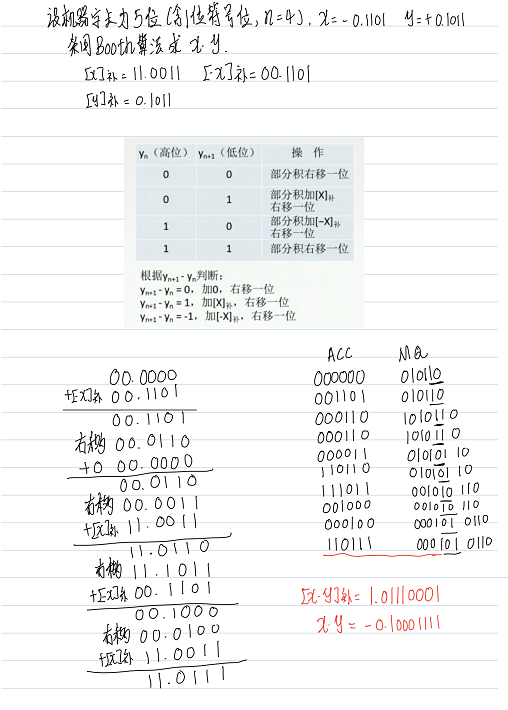

1.4.2 补码一位乘法

补码乘法以5次加法结束

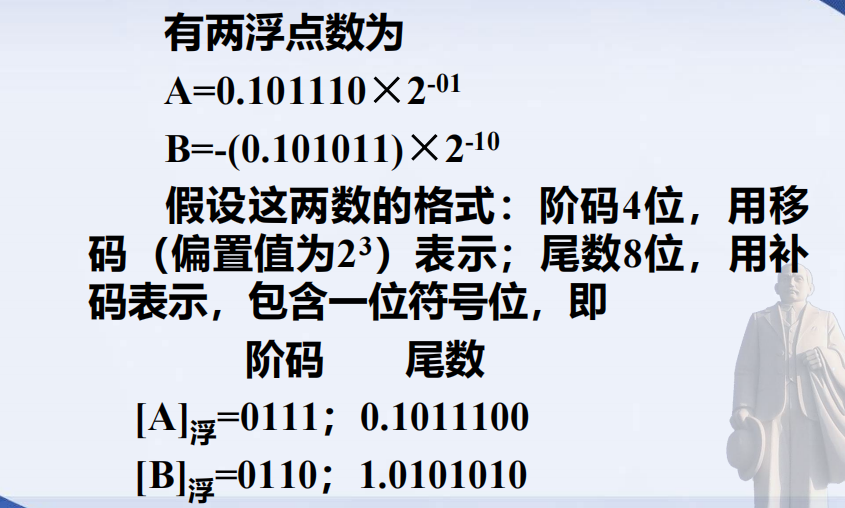

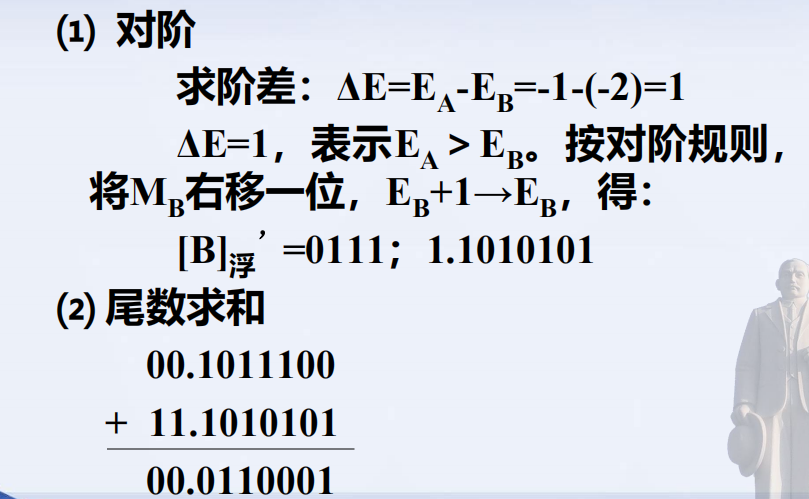

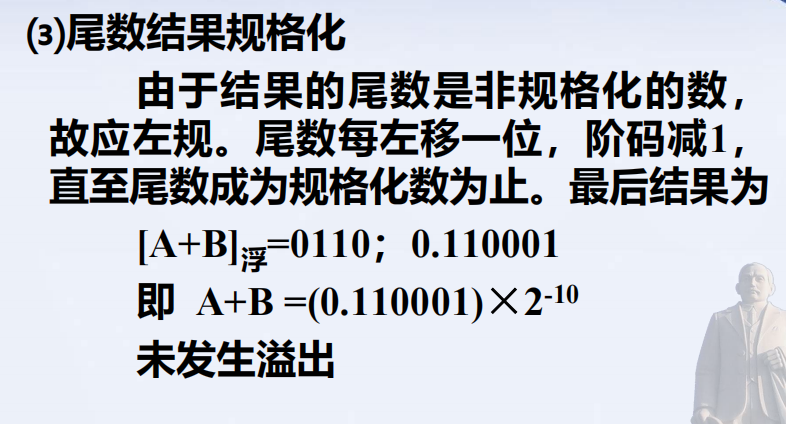

1.5 规格化浮点运算

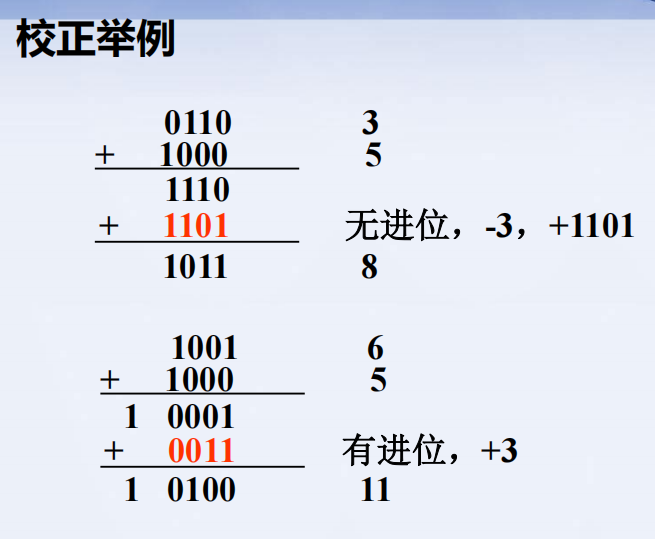

1.6 十进制整数的加法运算

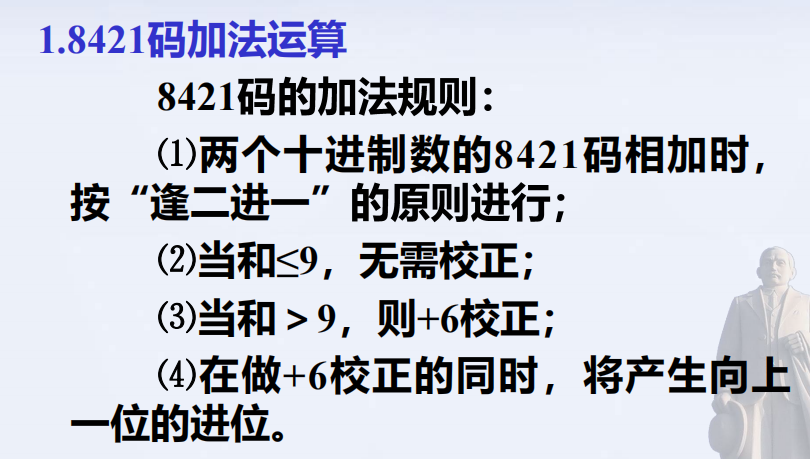

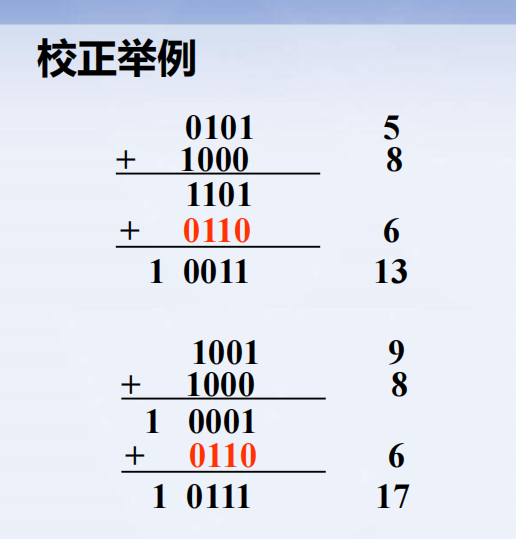

1.6.1 8421码加法运算

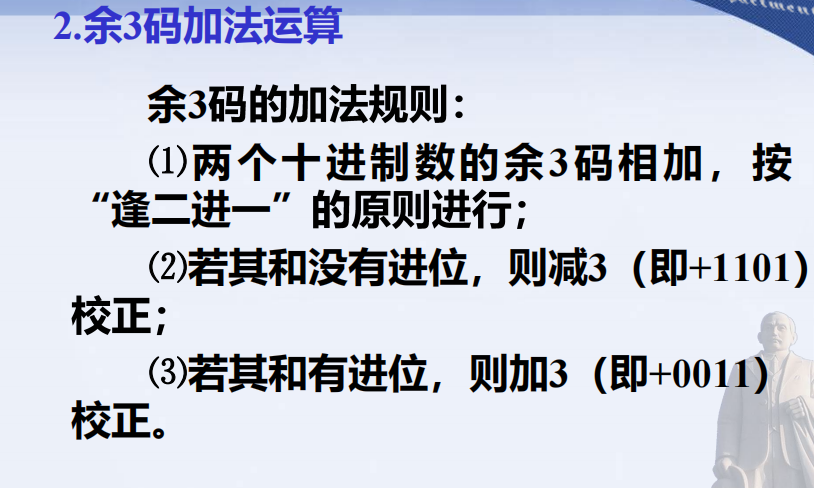

1.6.2 余3码加法运算

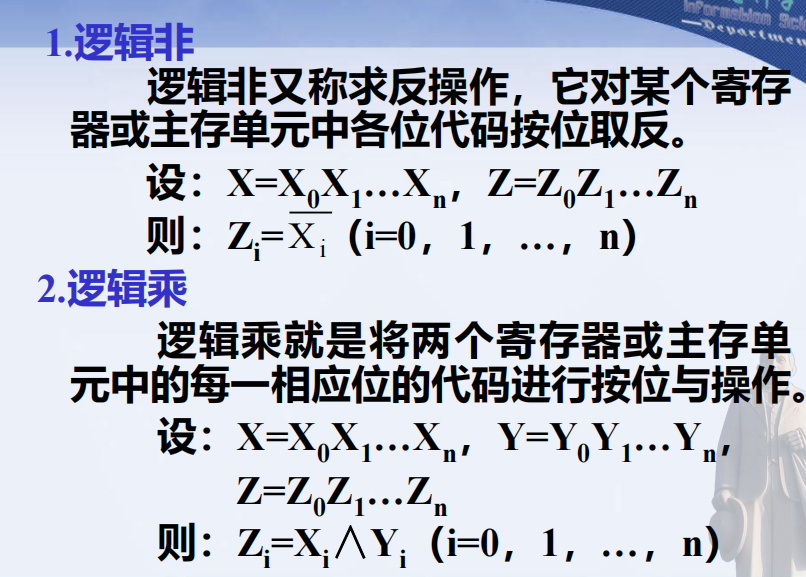

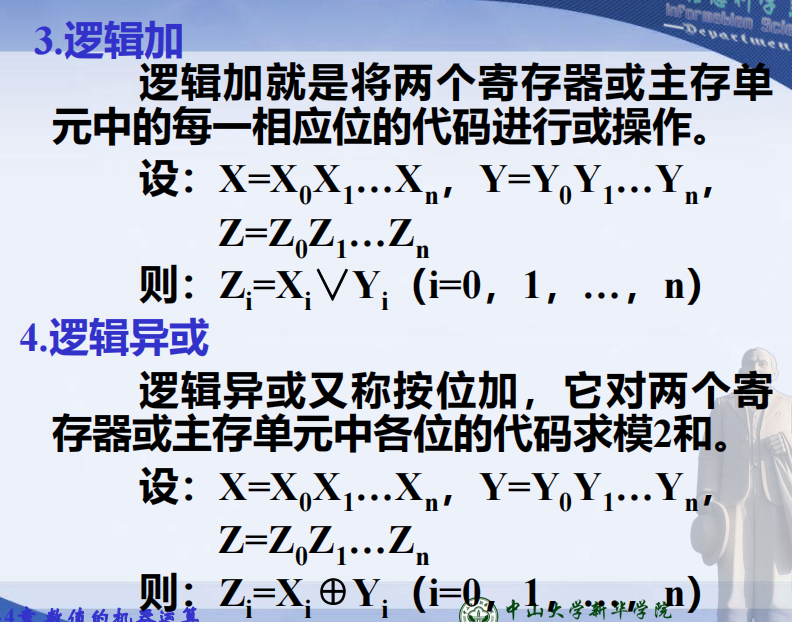

1.7 逻辑运算和实现

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/68621.html