module paobiao( input clk, input clr, input pause, output reg [3:0]msh,msl,sh,sl,mh,ml ); reg cn1,cn2;//cn1为百分秒向秒的进位,cn2为秒向分的进位 //百分秒进位 always @(posedge clk or negedge clr)begin if(!clr)begin {msh,msl}<=8'd0; cn1<=0; end else if(!pause)begin if(msl==4'd9)begin msl<=4'd0; if(msh==4'd9)begin msh<=4'd0; cn1<=1'b1; end else msh<=msh+1'b1; end else begin msl<=msl+1'b1; cn1<=1'b0; end end else {msh,msl}<={msh,msl}; end //秒进位 always @(posedge cn1 or negedge clr) begin if(!clr)begin cn2<=1'b0; {sh,sl}<=8'b0; end else if(sl==9)begin sl<=4'd0; if(sh==4'd5)begin sh<=4'd0; cn2<=1'b1; end else sh<=sh+1'b1; end else begin sl<=sl+1'b1; cn2<=1'b0; end end //分计数,满60自动清零 always @(posedge cn2 or negedge clr)begin if(!clr)begin {mh,ml}<=8'd0; end else if(ml==9)begin ml<=4'd0; if(mh==4'd5) mh<=4'd0; else mh<=mh+1'b1; end else ml<=ml+1'b1; end endmodule 讯享网

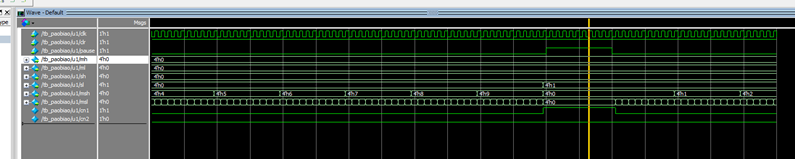

讯享网`timescale 1ns/1ns module tb_paobiao(); reg clk; reg clr; reg pause; wire[3:0]msh,msl,sh,sl,mh,ml; paobiao u1(.clk(clk),.clr(clr),.pause(pause),.msh(msh),.msl(msl),.sh(sh),.sl(sl),.mh(mh),.ml(ml)); initial begin clk<=1'b0; clr<=1'b0; pause<=1'b0; #50 clr<=1'b1; #1000 pause<=1'b1; #100 pause<=1'b0; end always #5 clk<=~clk; endmodule

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/64604.html