1、JTAG抓取波形报错:

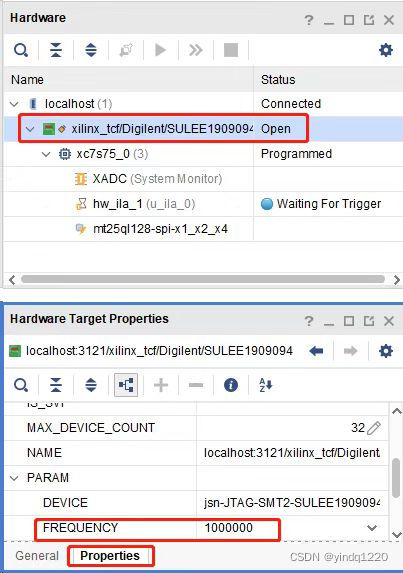

1、烧写器的JTAG时钟必须小于ILA输入时钟的2.5倍。可以根据实际工程情况,设置烧写器的JTAG时钟大小,位置如下图。

2、赛灵思 MPSOC系列FPGA 插上JTAG时,ARM会产生死机或者SPI读取数据不正确的情况,CPU读取SPI数据异常问题解决。

Zynq UltraScale+ MPSoC在未插JTAG情况下,ARM运行Linux系统正常,不会出现卡死现象,EMIO SPI读数正常。

当插上JTAG准备调试时,ARM会出现卡死现象,并且大多数情况下ARM通过EMIO SPI接口读取的数据会不正确

解决方法是:

a、上电启动后,即通过串口调试工具,比如SecureCRT软件快速按任意键,进入U-boot,当显示 "ZynqMP>"表示进入U-boot。此时输入指令关闭CPU_IDLE:

setenv bootargs 'console=ttyPS0,n8 earlycon clk_ignore_unused cpuidle.off=1'讯享网

b、继续进入系统

讯享网run bootcmd

c、使用JTAG正常调试即可。

3、vivado一直综合失败,但是语法无错误。

另外怀疑*mark_debug="TRUE”*也有影响

4、FPGA引脚上电默认电平的设置。

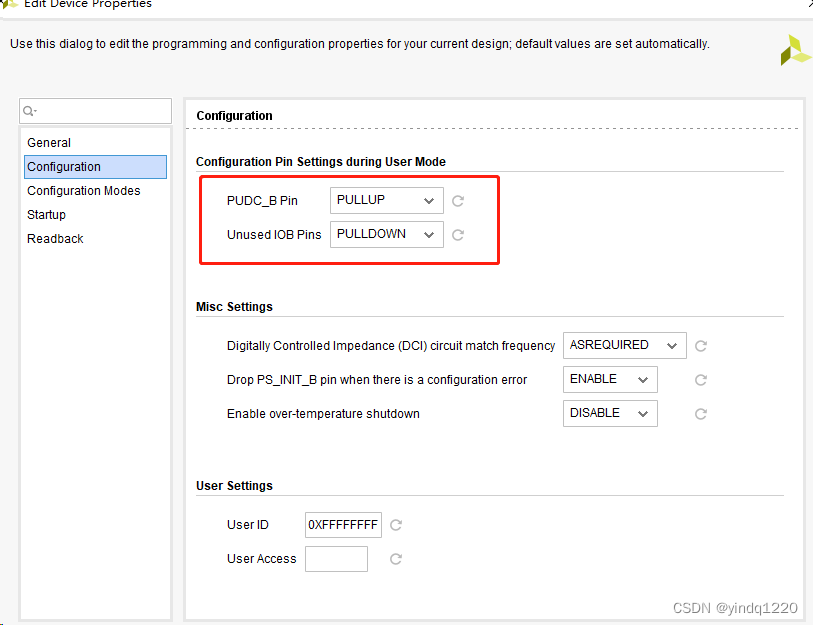

赛灵思FPGA上电默认电平可以由引脚PUDC_B控制。当PUDC_B为低电平时,fpga引脚都通过内部电阻上拉;为高电平时,不通过内部电阻上拉。

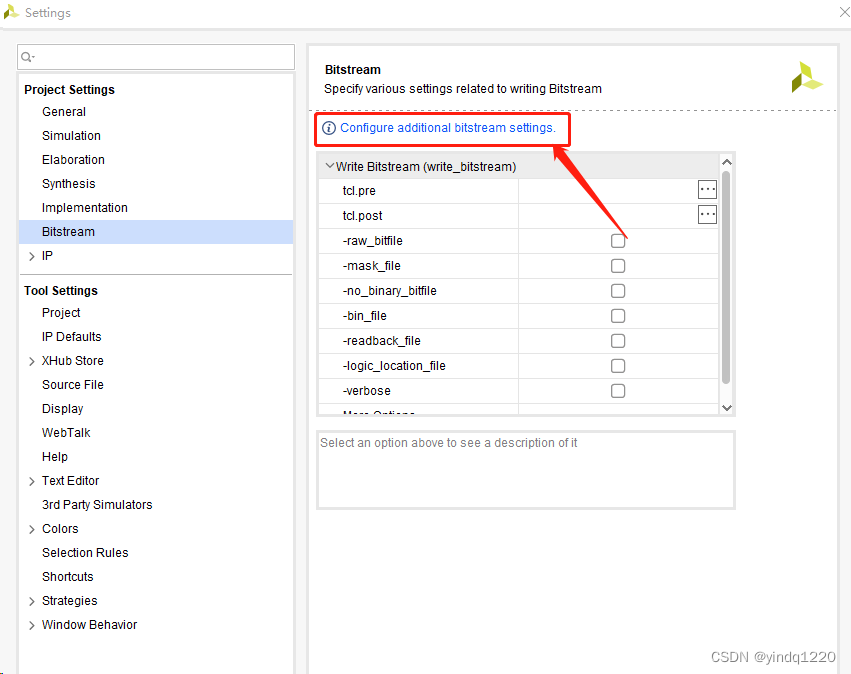

vivado软件工具中,也可以先 Open implemented Design,打开之后,在Tool-setting路径下,点击Configure additional bitstream settings.

在下图中,选择PUDC_B的上拉与否,以及未使用IO的默认电平。

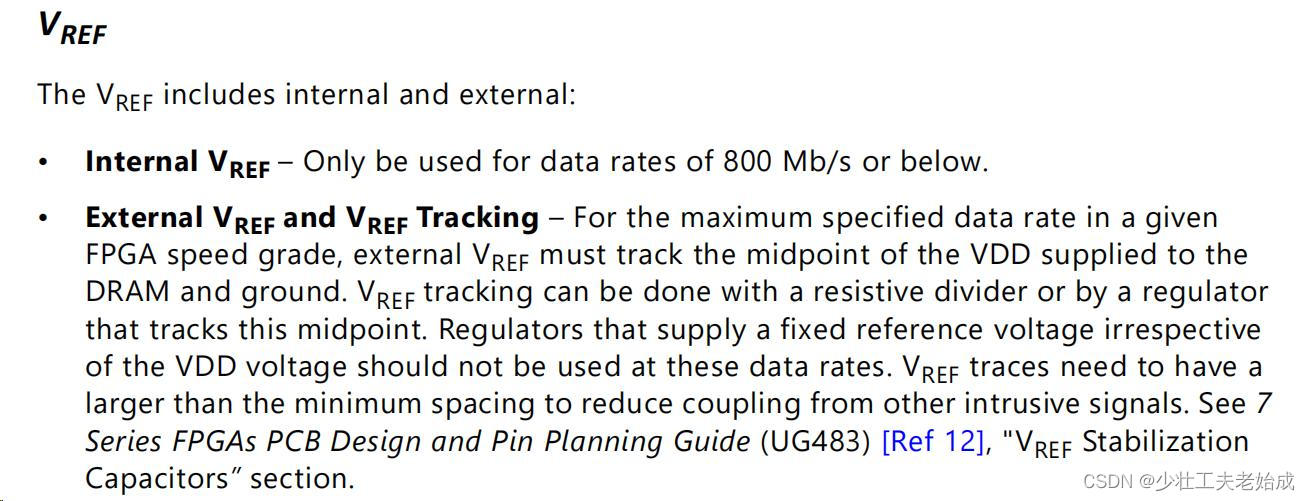

5、使用Spartan7 FPGA调试DDR3时,vivado MIG IP核校准失败 : init_calib_complete=0。打开IP的debug模式后,使用探针发现,dbg_wrcal_err = 1

该问题起初认为是硬件电路问题或者是DDR型号选择错误,经过多次测试后,一直未能解决问题。最终发现,是参考电压Vref选择错误。

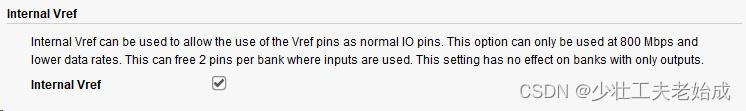

FPGA硬件原理图上, 连接DDR3数据信号的 BANK,若其VREF(比如引脚IO_L6N_T0_VREF_34_R6.......)信号未连接参考电压,FPGA应该使用internal Vref。在我们的设计中,硬件上VREF引脚悬空 ,因此在vivado上,应该勾选internal Vref。如下图:

set_property INTERNAL_VREF 0.750 [get_iobanks 34]

set_property INTERNAL_VREF 0.750 [get_iobanks 36]

6、Xilinx异步时钟约束

进行异步约束时,vivado经常报出关键性警告:

set_clock_groups:No valid object(s) found for '-group [get_clocks *clk2*]'.

Resolution: Check if the specified object(s) exists in the current design. If it does, ensure that the correct design hierarchy was specified for the object. If you are working with clocks, make sure create_clock was used to create the clock object before it is referenced.

这是约束语言未编写正确导致的。下面记录一下正确的编写方式。

假设顶层模块如下

module top ( ... ); Clk_gen clk_gen_inst0 ( .... .clk_100M(clk_100M), .clk_200M(clk_200M), .... ) endmodule正常的异步时钟约束如下:

讯享网#时钟命名,时钟约束 create_clock -period 10.000 -name clk_100M -waveform {0.000 5.000} [get_ports clk_gen_inst0/clk_100M] create_clock -period 5.000 -name clk_200M -waveform {0.000 2.500} [get_ports clk_gen_inst0/clk_200M] #异步时钟约束 set_clock_groups -asynchronous -group [get_clocks clk_100M] -group [get_clocks clk_200M] #或 set_clock_groups -asynchronous -group [get_clocks {clk_100M clk_200M}]

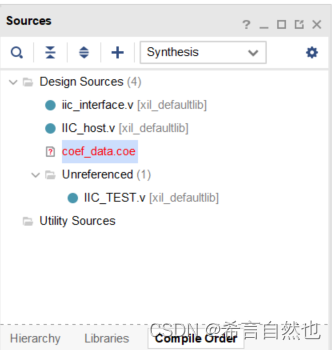

7、vivado编译报错:[Vivado 12-172] File or Directory 'C:/Users/15253/Desktop/project_fir/project_1.srcs/sources_1/ip/fir_compiler_0/coef_data.coe' does not exist

原因是,内置COE文件的相关IP被删除后,vivado没有自动将coe文件从编译列表中移除,手动删除即可。

选中coe文件,右击---remove file from project。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/39289.html