目录

SPI接口介绍

STM32上的NSS

NSS引脚的使用和配置

软件管理NSS

硬件管理NSS

SPI接口介绍

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是Motorola公司推出的一种高速的,全双工,同步的通信总线。

SPI总线共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

- NSS:从设备使能信号,由主设备控制,低电平有效

- SCK:时钟信号,由主设备产生

- MOSI:主设备输出从设备输入信号

- MISO:主设备输入从设备输出信号

STM32上的NSS

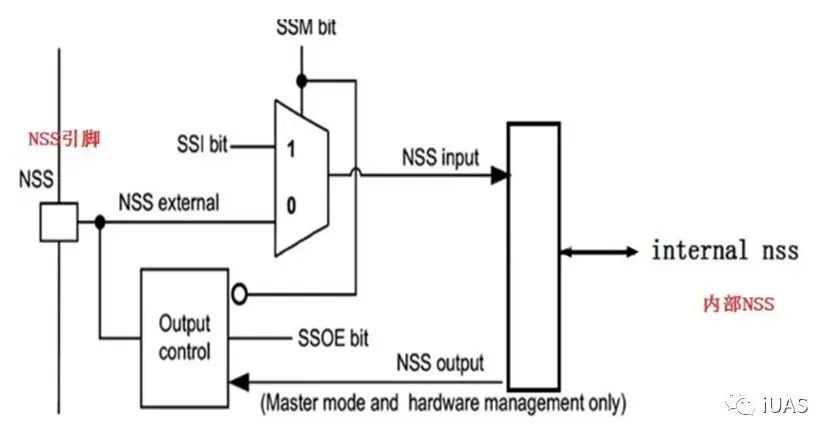

STM32上SPI接口的NSS结构图如图1所示,除了外部的NSS引脚,还有内部NSS,且内部NSS状态可以由寄存器独立控制,也正因此,NSS引脚既可作输入也可作输出。

图1 NSS结构图

NSS引脚的使用和配置

STM32上对NSS引脚的管理提供了软件管理和硬件管理两种方式,可以通过SPI_CR1寄存器中的SSM位设置这两种方式:

软件管理NSS

将SPI_CR1寄存器的SSM位置1即可设置该模式。

此时,从器件选择信息在内部由SPI_CR1寄存器的SSI位的值驱动。外部的NSS引脚空闲,可作为普通GPIO使用。

实际应用中,该模式下,若STM32端的SPI作为主设备使用,需将SSI位置1,此时,可以用任意普通GPIO输出高低信号控制从设备的片选;若为从设备,则需将SSI位清零。

硬件管理NSS

将SPI_CR1寄存器的SSM位清零即可设置该模式。

此时,通过设置SPI_CR1寄存器的SSOE位,硬件管理NSS又有以下两种模式:

- 输出使能(SSOE=1)

仅当器件为主模式时才使用此配置。当主器件开始通信时,会驱动NSS引脚为低电平,直到SPI被关闭为止。

- 输出禁止(SSOE=0)

对于在主模式下工作的器件,此配置允许多主模式功能,此时应使用GPIO控制从机的片选。

对于设置为从模式的器件,NSS引脚用作传统的片选输入,在NSS引脚为低电平时片选该器件,为高电平时,取消对该器件的片选。

实际应用中,若配置为主模式,希望通过主机的NSS引脚硬件自动片选从设备,还需在硬件上对NSS引脚设计上拉,以保证主机SPI关闭时,NSS引脚为高电平。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/31956.html