<svg xmlns="http://www.w3.org/2000/svg" style="display: none;"> <path stroke-linecap="round" d="M5,0 0,2.5 5,5z" id="raphael-marker-block" style="-webkit-tap-highlight-color: rgba(0, 0, 0, 0);"></path> </svg> <p><img src="https://img-blog.csdnimg.cn/.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3dsd2wwMDcxOTg2,size_16,color_FFFFFF,t_70" alt="" /></p> 讯享网

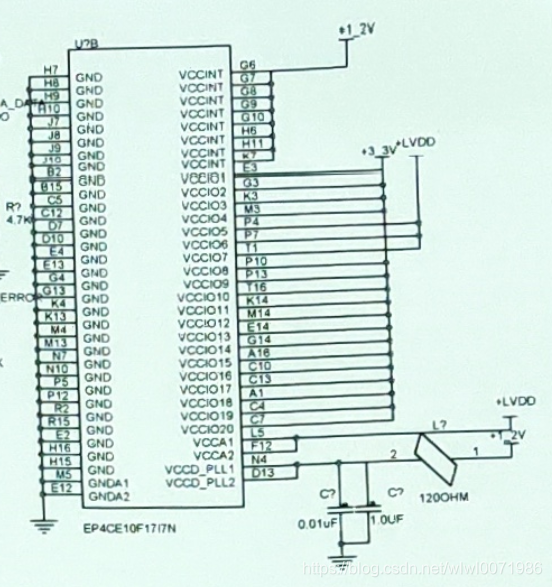

FPGA的功能引脚包含了FPGA配置程序加载、FPGA配置模式选择、状态及错误提示、JTAG调试等等。

DCLK、DATA0、NCONFIG、CONF_DONE这几个引脚是配置FPGA所必须的,DATA1~DATA7可以用作其他功能,INIT_DONE可以不使用。TDI、TDO、TMS、TCK四个脚是JTAG调试使用,一般会预留。

- IO引脚

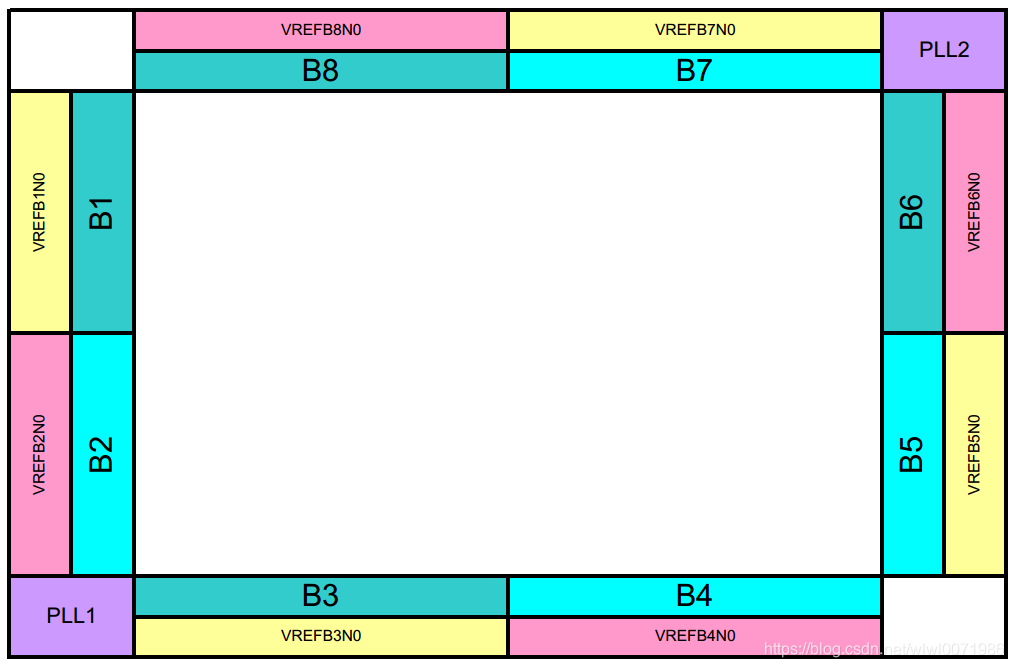

FPGA的IO引脚是芯片与外部电路的接口部分,完成在不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA的IO引脚按组分类,每组都能够独立地支持不同的IO标准。通过软件的灵活配置,可适配不同的电气标准与IO物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。为了便于管理和适应多种电器标准,FPGA的IO引脚被划分为若干个Bank,每个BANK的接口标准由其接口电压VCCIO决定。

一个BANK只能有一种VCCIO,但不同的BANK的VCCIO可以不同,只有相同电气标准的端口才能接到一起。

- FPGA的电源和接地引脚

电源引脚为不同的电气需求提供不同的电压,包括VCCINT、VCCIO、VCCA、VCCD_PLL等。不同的BANK可以使用不同的IO电压,也可以连在一起使用相同的IO电压。接地引脚可以全部连在一起接到GND上。

二、FPGA的配置方式

- 配置方案

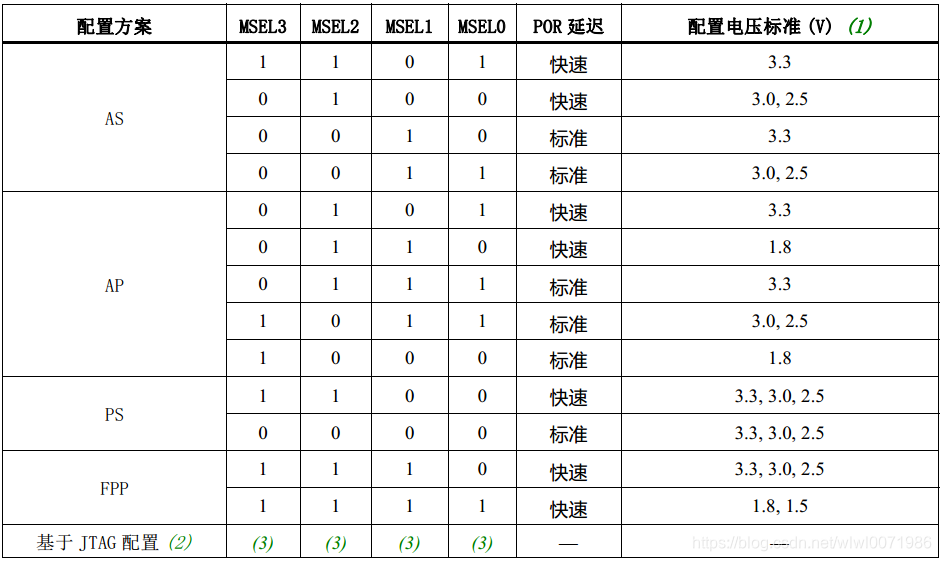

FPGA有以下几种配置方案:

主动串行(AS)

主动并行(AP)

被动串行(PS)

快速被动串行(FPP)

JTAG模式

硬件上通过连接MSEL四个引脚的组合方式来选择使用哪种模式,主流方案使用的是被动串行配置(PS)方案。

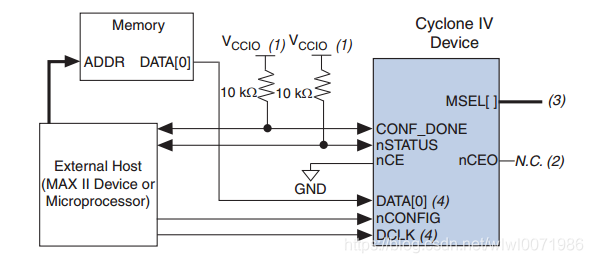

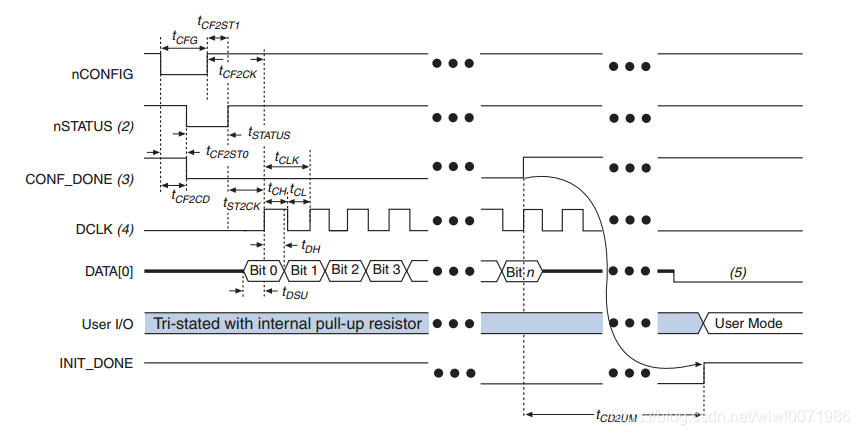

- 使用PS方式配置FPGA

在 PS 配置方案中,可以使用微处理器控制从存储器件 (例如闪存)传输配置数据到目标 Cyclone IV 器件。可以将配置数据存储

为 .rbf、 .hex 或 .ttf 的格式。

(1)当其nCONFIG引脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态引脚nSTATUS和CONFIG_DONE引脚也将输出为低。

(2)当FPGA的nCONFIG引脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路输出的nSTATUS引脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。

(3)FPGA在 DATA[0] 上接收配置数据,在 DCLK 上接收时钟。在 DCLK 的上升沿,数据被锁存到器件中。数据不断送入目标器件,直到 CONF_DONE 变高以及器件进入初始化状态。

(4)主控必须一次一个位地将配置数据放置在 DATA[0] 上。如果使用的配置数据格式为 .rbf、 .ttf 或 .hex,必须首先发送每个数据字节的 LSB。例如,如果 .rbf 包含的字节序列为 02 1B EE 01 FA,那么必须发送到器件的串行比特流是 : 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111

(5)当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。

(6)CONF_DONE引脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

(7)INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该引脚。这个引脚不是必须使用的,很多FPGA方案中没有使用这个引脚。

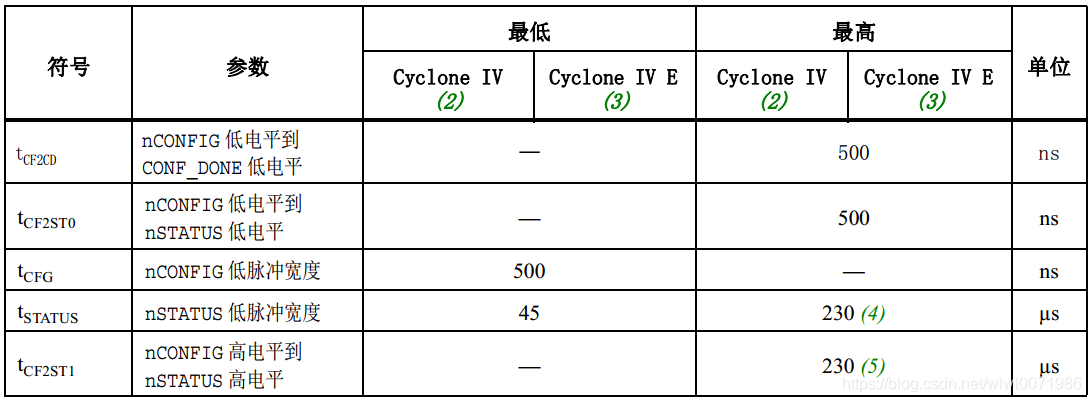

- FPGA时序参数

三、FPGA和外界数据通讯接口

FPGA除了对IO引脚进行控制外,还可以和外界数据进行通讯。

- GPCM模式

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/195435.html