有两种途径可以实现工艺特征尺寸进入到小于25nm工艺制程:

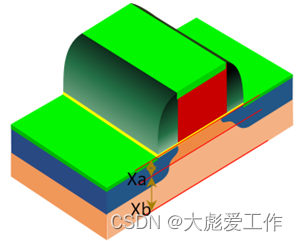

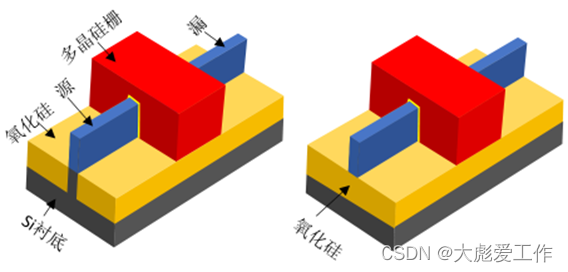

一种是采用三维立体型结构的FinFET晶体管代替平面结构的MOSFET作为集成电路的晶体管。FinFET晶体管凸起的沟道区域是一个被三面栅极包裹的鳍状半导体。沿源-漏方向的鳍与栅重合区域的长度为晶体管沟道长度。

另外一种是基于SOI的超薄绝缘层上的平面硅技术,称为UTB-SOI,也就是FD-SOI晶体管,研究发现要使UTB-SOI正常工作,绝缘层上硅膜的厚度应限制在栅长的四分之一左右。对于25nm栅长的晶体管,UTB-SOI的硅膜厚度应被控制在6nm左右。

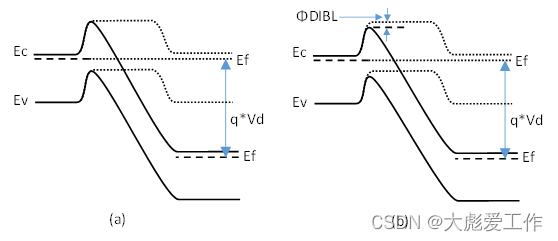

为什么FD-SOI和FinFET要把沟道的厚度制造的很薄,它的原理是什么呢?

(1)沟道距离栅极Xa≤0.25*Lg的沟道区域的能带图,栅极对该区域的沟道形成有效的控制,漏端的电压Vd不足以导致沟道的势垒高度降低。

相关内容

《【半导体先进工艺制程技术系列】应变硅工艺技术》

《【半导体先进工艺制程技术系列】HKMG工艺技术(上)》

《【半导体先进工艺制程技术系列】HKMG工艺技术(下)》

《【半导体先进工艺制程技术系列】SOI技术(上)》

《【半导体先进工艺制程技术系列】SOI技术(中)》

《【半导体先进工艺制程技术系列】SOI技术(下)》

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/17610.html