一、RISC-V的特权级别

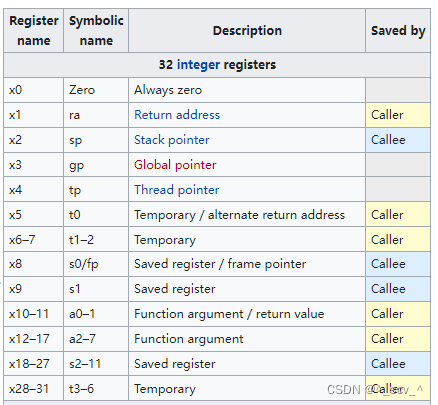

riscv的特权级别一共有3种,每个riscv架构的芯片,至少包含其1种特权等级。其3种特权级别如下图所示:

其中机器模式具备最高级别的特权等级,运行在此模式下的代码被认为是天然可信的;而用户模式则仅具备部分的特权等级,一般在此模式下运行的代码是操作系统中的应用代码。

所有的riscv架构的芯片,必须实现机器模式,在此模式下,它可以直接访问到计算器底层的硬件。

二、RISC-V寄存器说明

riscv架构具备非特权寄存器和特权寄存器;其中非特权寄存器顾名思义,就是指在任何特权模式下都可访问的寄存器;特权寄存器则指需要在某些特权模式下才能够访问到的寄存器。

其中某些寄存器具备通用性质,所以被称为通用目的寄存器;另外一些寄存器被用于控制CPU的功能以及表示其相应状态,被称为控制状态寄存器。

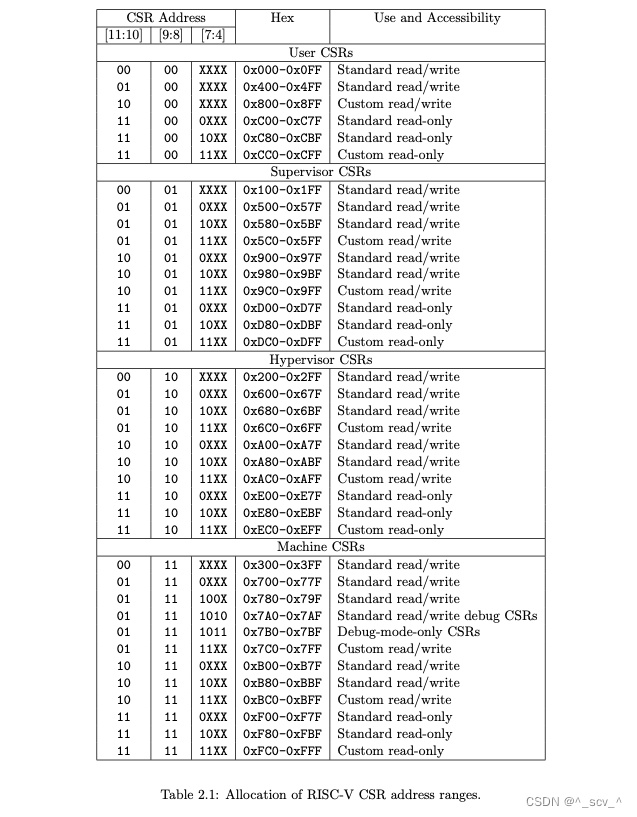

1、通用目的寄存器

通用目的寄存器有32个,即x0~x31,如下图所示:

其中x0寄存器的值始终为0;x1与x2寄存器在标准软件中约定,用于作为函数调用的返回地址存储寄存器和栈地址寄存器(这里说的约定,就是指这两个寄存器并不是专用于这两个作用的,只是我们约定俗成的)。

同时还有一个额外的非特权寄存器:程序计数器pc,保存当前指令的地址。

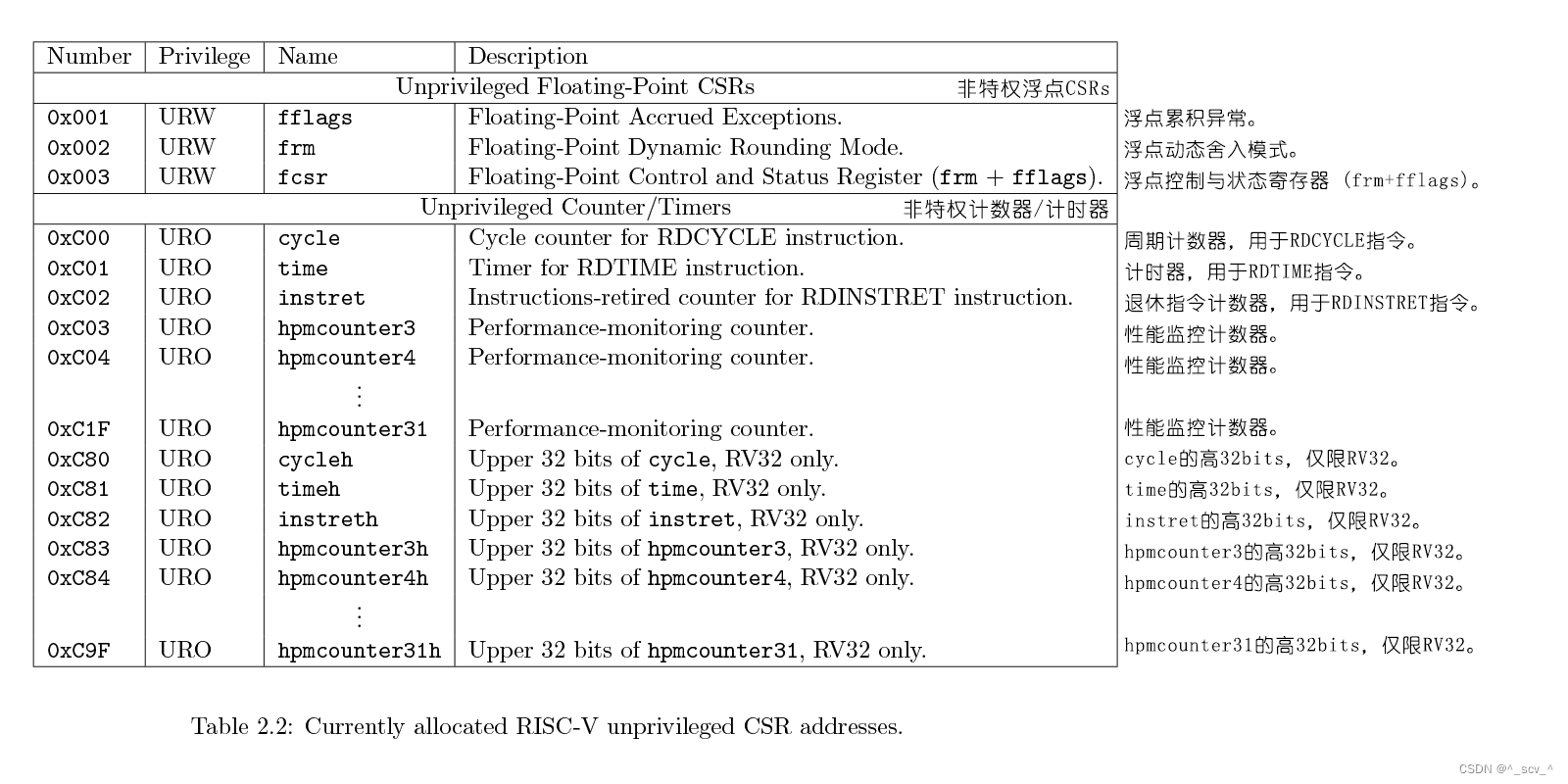

2、控制状态寄存器

标准的riscv架构,预留了12bit的编码空间,用于编码4096个控制状态寄存器(即CSR)。其中csr[11:10]用于指示此csr寄存器的可读可写模式;csr[9:8]用于指示此csr寄存器可被访问的特权模式的等级。

当试图访问一个不存在的csr将会触发一个不合法的指令异常;以不恰当的特权等级去访问一个csr,或去写一个只读的csr时,也会触发非法指令异常。

如下图所示,此图说明了控制状态寄存器(CSR)的地址空间分配:

在riscv架构芯片的实现中,上述的CSR是必不可少的。其中已经有一部分的CSR寄存器被riscv标准预留作为固定功能使用了,剩下的部分空间,各个芯片厂商才能用于实现自己的CSR寄存器。

不过被riscv标准架构预留作为固定功能使用的CSR寄存器,各个芯片厂商可以不用完全实现,仅实现自己芯片部分用到的CSR寄存器功能即可。(如riscv架构中的标准定时器)

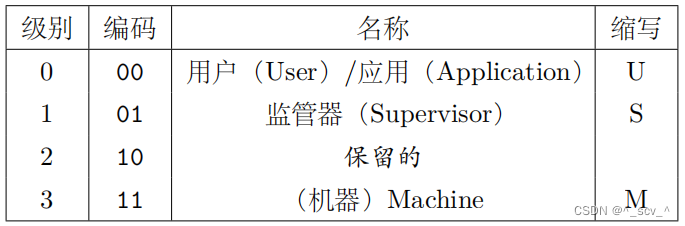

被预留的CSR部分寄存器如下图:

上图描述了对于用户模式下的非特权CSR寄存器的预留情况。如果想要进一步了解特权级的CSR寄存器预留情况,请在riscv架构手册中进行查询。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/123432.html