【From Accelerated to Operating Conditions: How Trapped Charge Impacts on TDDB in SiO2 and HfO2 Stacks】

文章总结:

本研究深入探讨了在SiO2和HfO2介质堆叠中,陷阱电荷对时间依赖介电击穿(TDDB)现象的影响。通过引入载流子注入(CI)模型,并结合多尺度模拟工具Ginestra®,研究者们提供了一个更为全面的TDDB现象解释,并准确预测了在操作条件下的介电击穿寿命。研究发现,陷阱电荷的存在显著改变了TDDB寿命预测,这一影响在低电压下尤为显著,而在高电压下则可以忽略不计。此外,研究还揭示了陷阱电荷与介质堆中缺陷前体的微观特性相结合时,对TDDB动态和漏电流的综合影响。

研究背景:

现代电子设备中,基于互补金属氧化物半导体(CMOS)技术的介电击穿是关键的失效机制之一。尽管已有多种理论模型能够描述加速条件下的介电击穿实验趋势,但它们在预测操作条件下的设备寿命时存在显著差异。因此,研究者寻求一个统一的模型,能够准确预测不同材料系统中操作条件下的设备寿命。

研究目的:

本研究旨在通过将陷阱电荷的影响纳入CI模型,提供一个更为完整的介电击穿现象描述,并准确估计SiO2和HfO2介质堆在操作条件下的介电击穿寿命。同时,研究探索了陷阱电荷与缺陷前体的微观特性相结合时,对TDDB和氧化物中的漏电流的综合影响。

实验方法:

研究者使用了多尺度模拟工具Ginestra®进行TDDB分布的模拟。通过密度泛函理论(DFT)计算获取材料和缺陷前体的微观特性参数,并在模拟中考虑了不同的P位点热能(ETH)值,以研究它们对TDDB和漏电流的影响。模拟包括了多种传导机制,并考虑了电极工作函数、氧化物性质和厚度等因素。

模拟结果:

模拟结果显示,在低电压下,陷阱电荷显著延迟了SiO2中的TDDB过程,而在高电压下,其影响几乎可以忽略。相反,在HfO2中,陷阱电荷的存在加速了TDDB过程。此外,研究还发现,不同的ETH值对TDDB动态和漏电流有显著影响。

在SiO2中,陷阱电荷的存在通过屏蔽效应减缓了后续的电荷捕获过程,从而延迟了TDDB。而在HfO2中,由于存在多种电荷状态的缺陷,陷阱电荷的存在增加了局部电场,加速了电荷捕获过程和介电击穿。这些结果与随机电报噪声研究和实验数据相一致,证实了模拟方法的可靠性。

研究的创新点:

- 创新性地将陷阱电荷的影响纳入CI模型,提供了一个更为全面的介电击穿现象描述。

- 通过模拟揭示了陷阱电荷对TDDB寿命预测的显著影响,特别是在低电压条件下。

- 研究了不同材料系统中缺陷前体的微观特性对TDDB和漏电流的综合影响。

研究意义:

本研究对于理解和预测现代电子设备中介电材料的可靠性具有重要意义。通过准确估计介电击穿寿命,可以为器件设计和寿命预测提供更可靠的依据,进而指导未来的材料选择和工艺优化。此外,研究结果对于提高电子设备的稳定性和延长其使用寿命具有实际应用价值,特别是在低电压操作条件下。

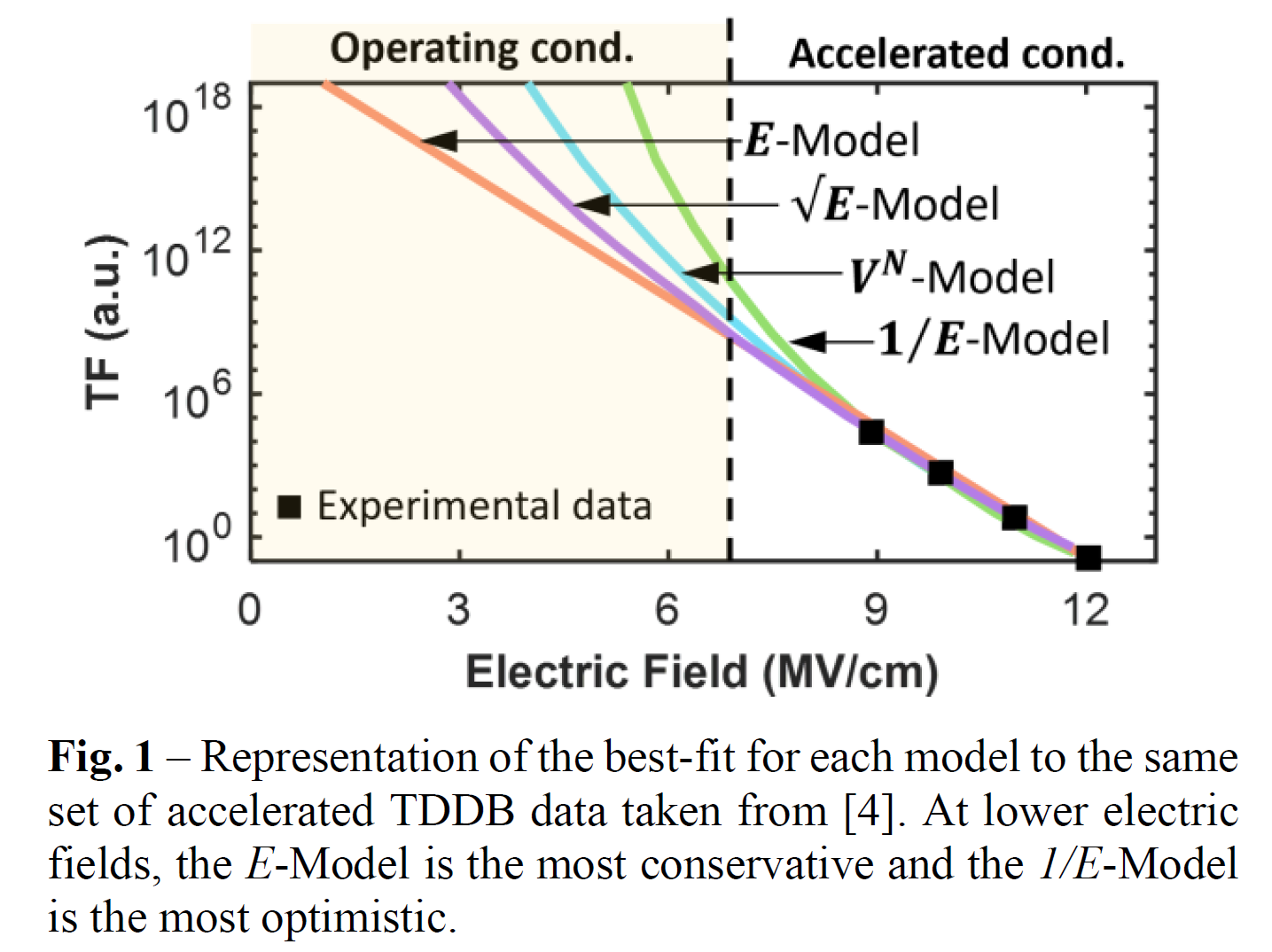

- 图 1:展示了不同模型对加速条件下TDDB数据的拟合情况。这些模型包括E-Model、1/E-Model等,它们在低电场下的表现有所不同,其中E-Model最为保守,而1/E-Model最为乐观。

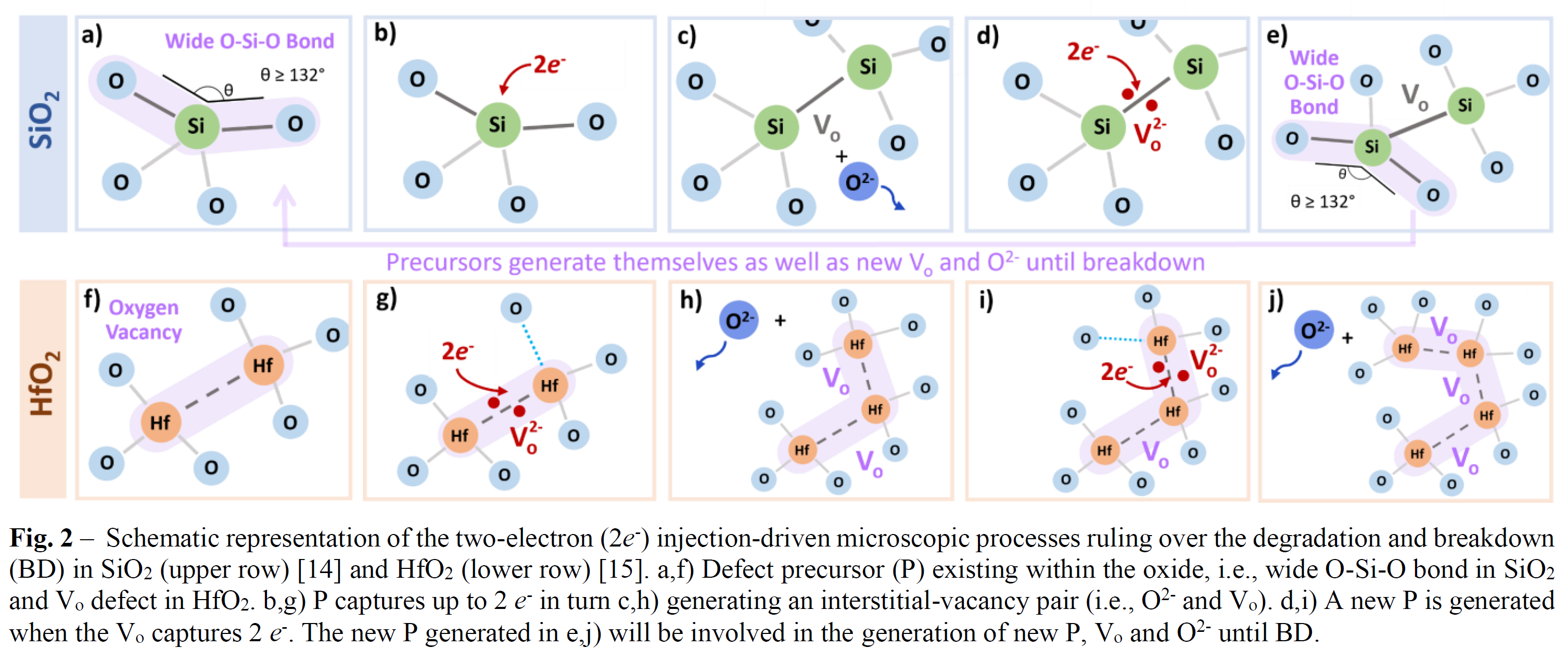

- 图 2:分别展示了SiO2和HfO2中缺陷前体和缺陷生成机制的示意图。图中详细描述了在SiO2中宽O-Si-O键作为缺陷前体,以及在HfO2中氧空位(Vo)作为最常见的缺陷前体。图中还展示了当这些缺陷前体捕获电子后,如何通过一系列过程形成Frenkel对(即中性Vo和氧离子O2-),进而影响材料的介电击穿。

- 图 3:通过模拟展示了在SiO2中,当存在和不存在附近捕获的2e-电荷时,P位点处的局部电势(VLOC)的变化。图中提供了在低和高VAPP(应用电压)条件下,通过P位点的2D电势图和1D局部电势剖面图,说明了捕获电荷对局部电势的影响。

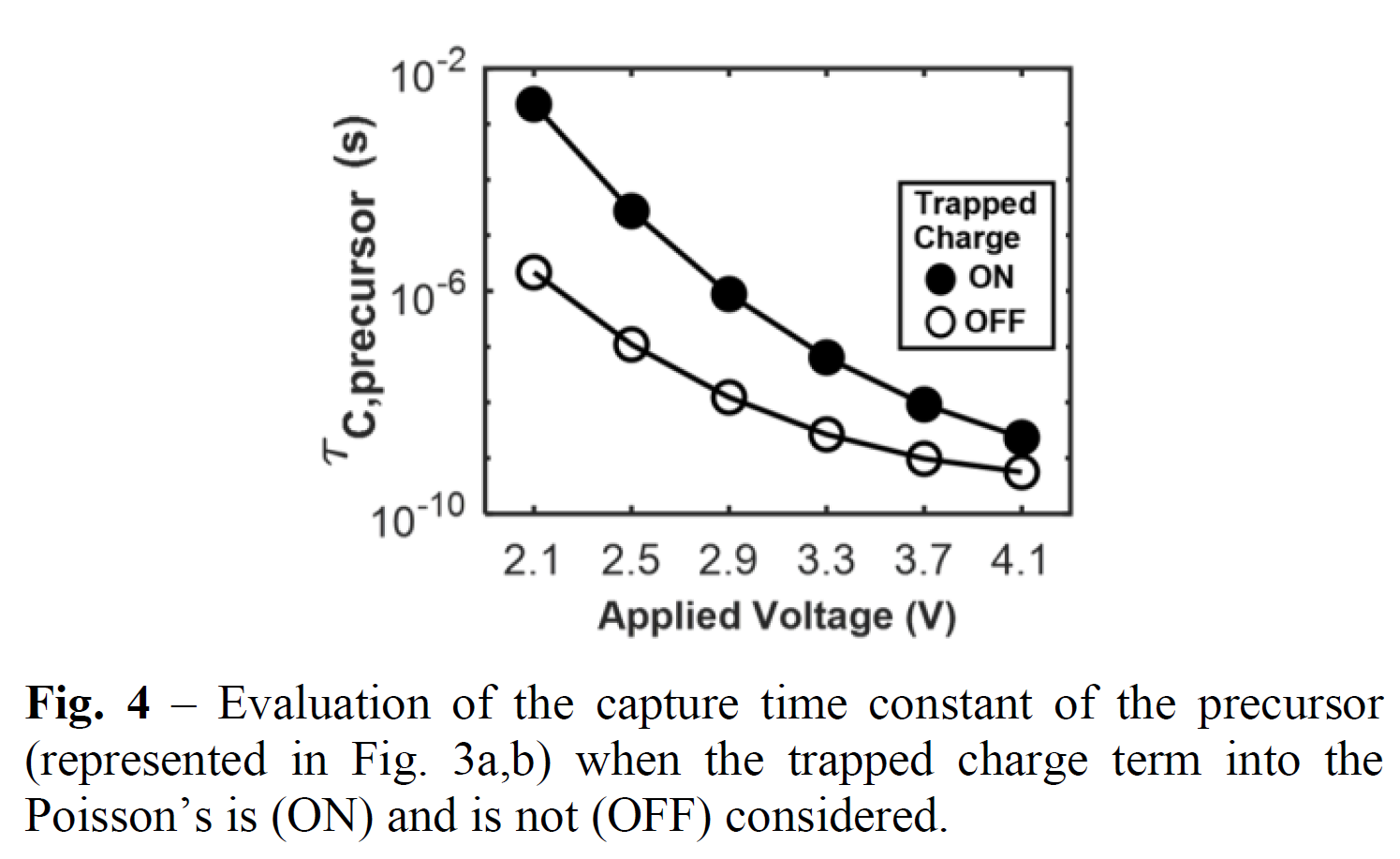

- 图 4:展示了在考虑和不考虑Poisson方程中的捕获电荷项时,P位点的捕获时间常数(τc)的评估。说明捕获电荷对介电击穿过程中电荷注入动力学的影响。

- 图 5:展示了用于模拟的TiN/SiO2/Si和TiN/HfO2/TiN器件堆叠的结构示意图。这些堆叠结构用于研究TDDB分布,并且展示了器件的面积和层厚等参数。

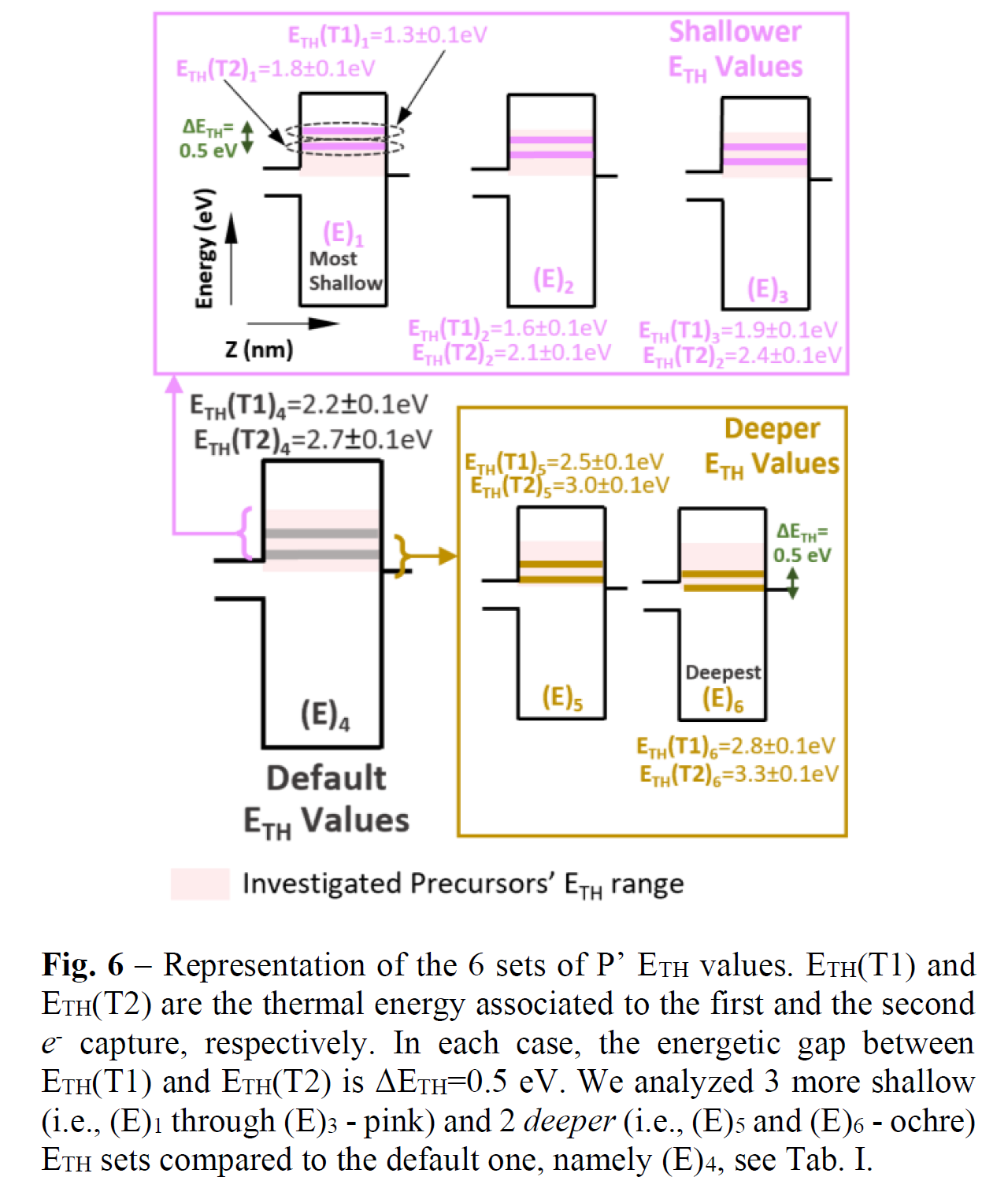

- 图 6:展示了用于模拟的P位点的热能(ETH)值的六组不同设置。图中解释了ETH(T1)和ETH(T2)分别与第一次和第二次电子捕获相关,并保持它们之间的能量差为0.5 eV。

- 图 7:展示了在SiO2基堆叠上进行的主要统计TDDB模拟结果,包括考虑和不考虑Poisson方程中捕获电荷项的情况。图中包括了电流与时间的模拟结果、Weibull图以及从Weibull图中提取的击穿时间与应用电压的关系。

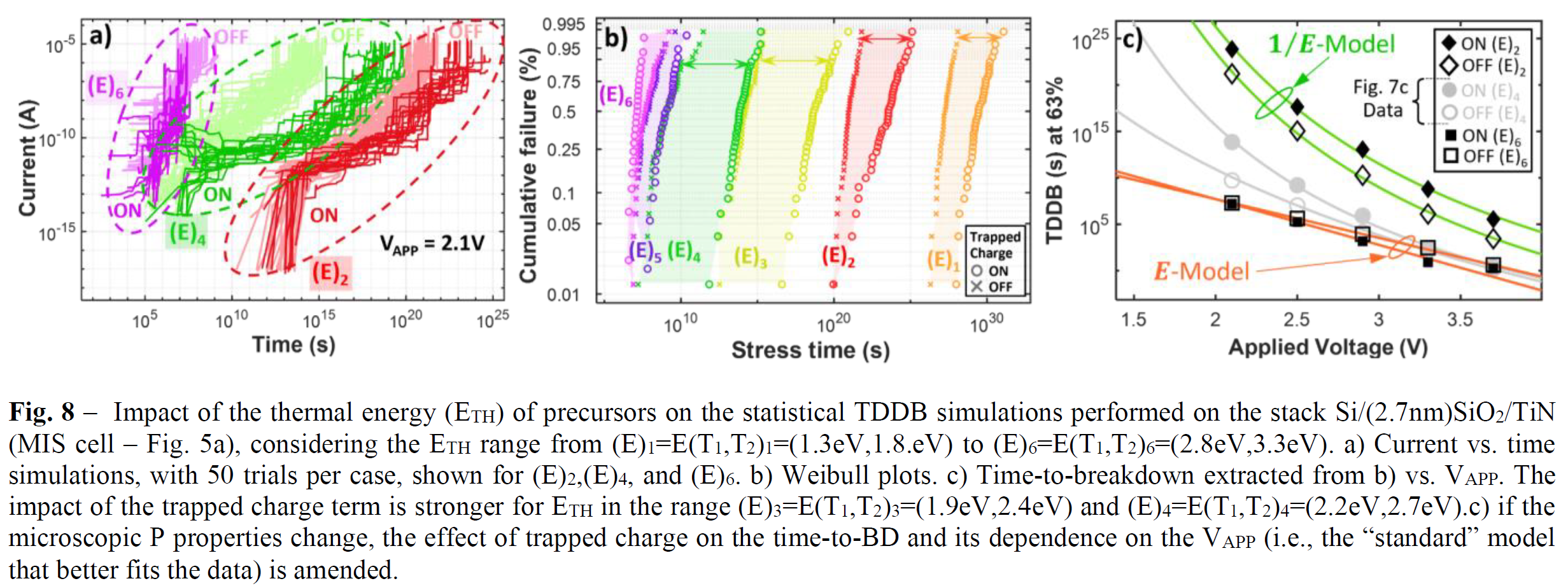

- 图 8:展示了在SiO2基堆叠上进行的统计TDDB模拟结果,这些结果考虑了不同的P位点热能(ETH)值。图中包括了电流与时间的模拟结果、Weibull图以及从Weibull图中提取的击穿时间与应用电压的关系。

- 图 9:展示了模拟数据与实验数据的对比。图中的模拟数据是基于考虑捕获电荷影响的CI模型,而实验数据来自于2.67nm SiO2 MOS电容的TDDB测量。

- 图 10:展示了在不同P位点热能(ETH)值下,对SiO2基堆叠的漏电流的影响。图中包括了在考虑和不考虑捕获电荷项的情况下,通过DC模拟得到的漏电流结果。

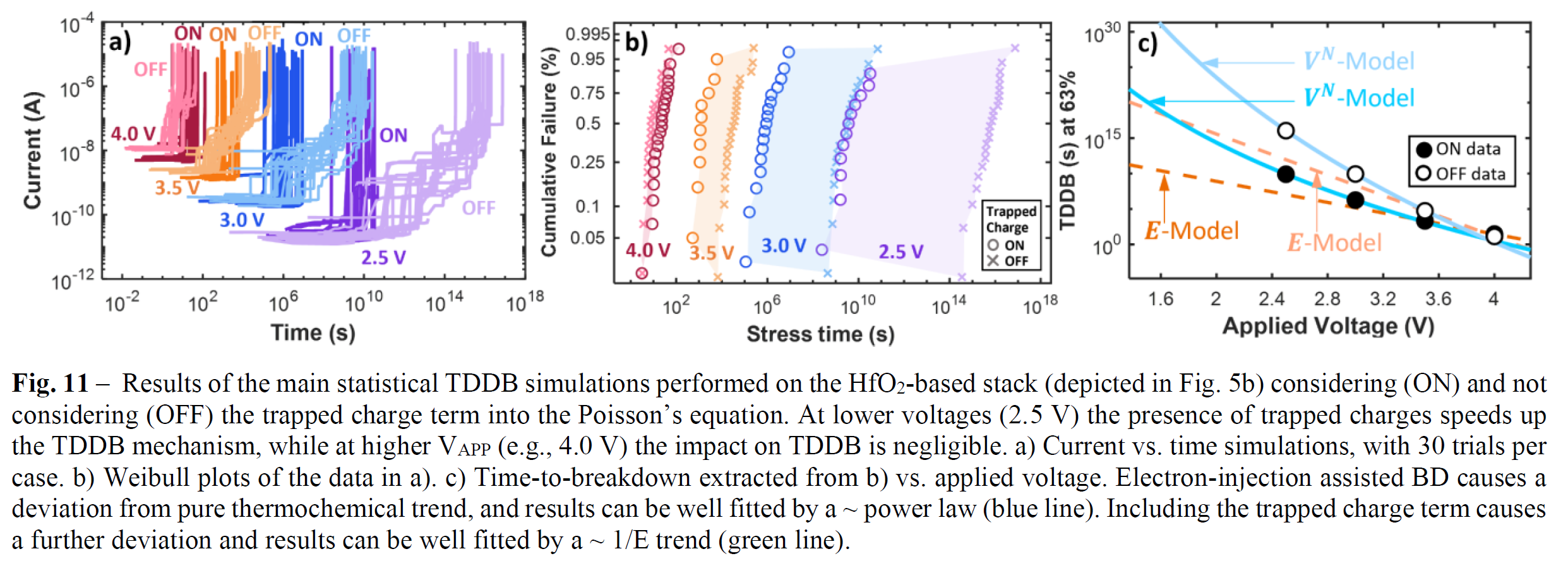

- 图 11:与图 7类似,但针对的是HfO2基堆叠的TDDB模拟结果。图中展示了考虑和不考虑捕获电荷项的情况下,电流与时间的模拟结果、Weibull图以及击穿时间与应用电压的关系。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/47987.html