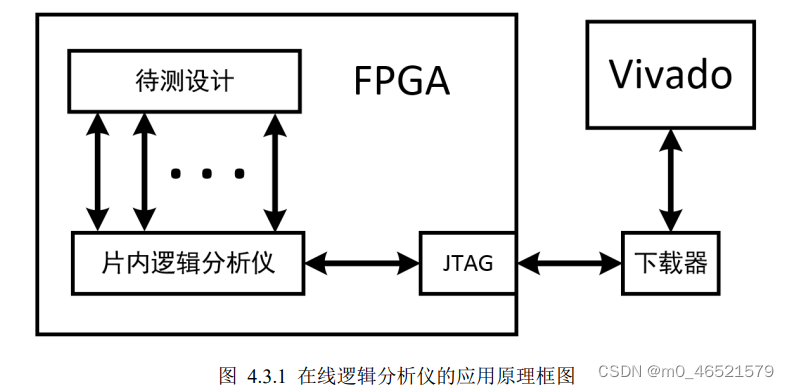

待测设计(Design Under Test,DUT)就是用户逻辑,它和片内的在线逻辑分析仪都位于 FPGA 中。

在线逻辑分析仪通过一个或多个探针(Probe)来采集希望观察的信号,然后通过片内的 JTAG 硬核组件,来将捕获到的数据传送给下载器,进而上传到 Vivado IDE 以供用户查看。

Vivado IDE 也能够按照上述 数据路径,反向地向 FPGA 中的在线逻辑分析仪传送一些控制信息。

在线逻辑分析仪会占用一定数量的内部逻辑资源,如块 RAM、查找表、触发器等等。

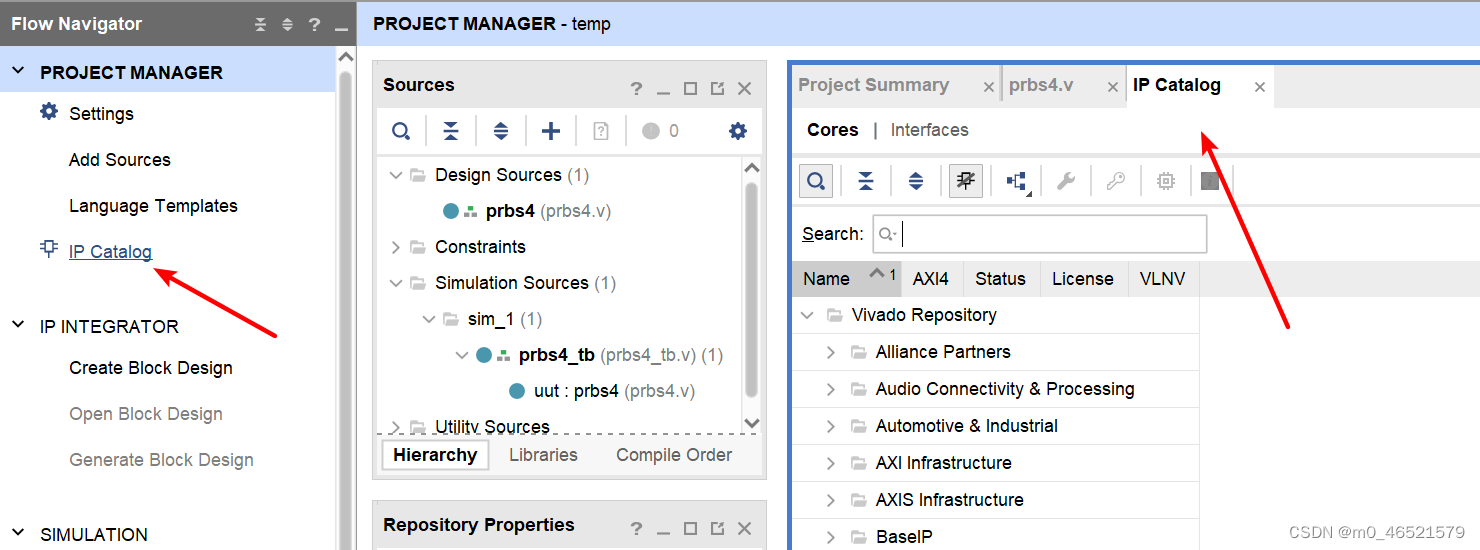

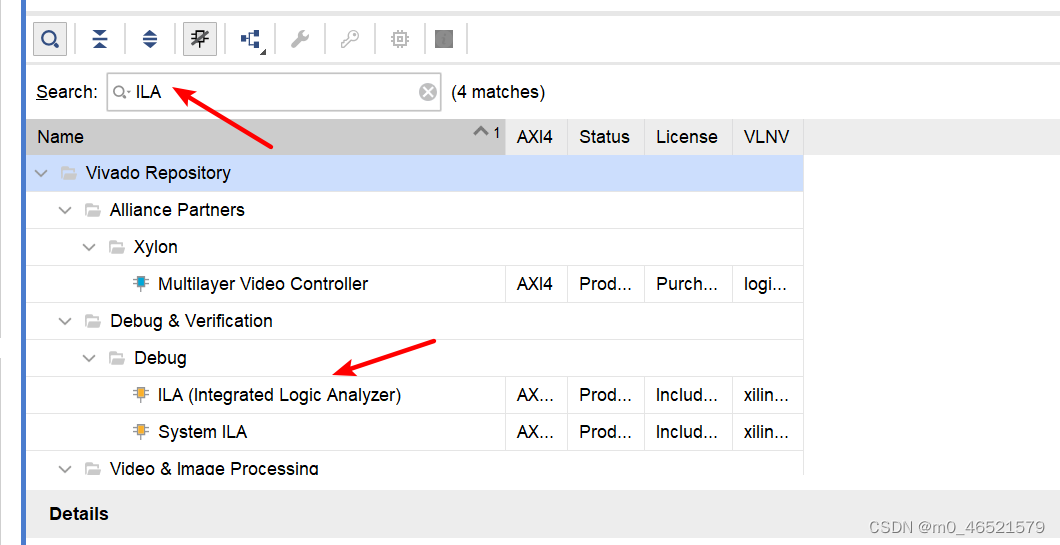

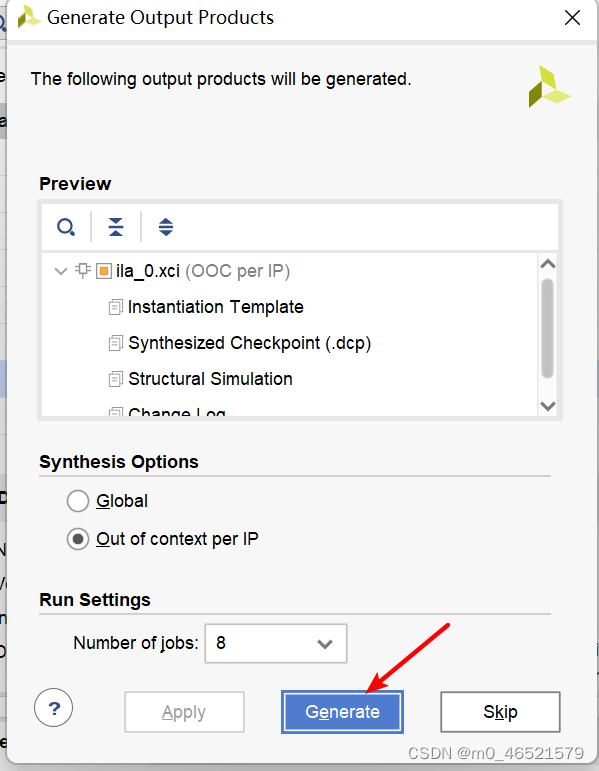

在Vivado中,在线逻辑分析仪的功能被称为集成逻辑分析器(Integrated Logic Analyzer,ILA),以IP核的形式来加入到用户设计中。Vivado提供了三种具有不同集成层次的插入ILA方法:(1)HDL实例化调试探针流程;(2)网表插入调试探针流程;(3)手动地在XDC约束文件中书写对应的Tcl XDC调试命令,在实现阶段工具会自动读取这些命令,并在布局布线时加入这些ILA IP核。

一、HDL实例化调试探针流程

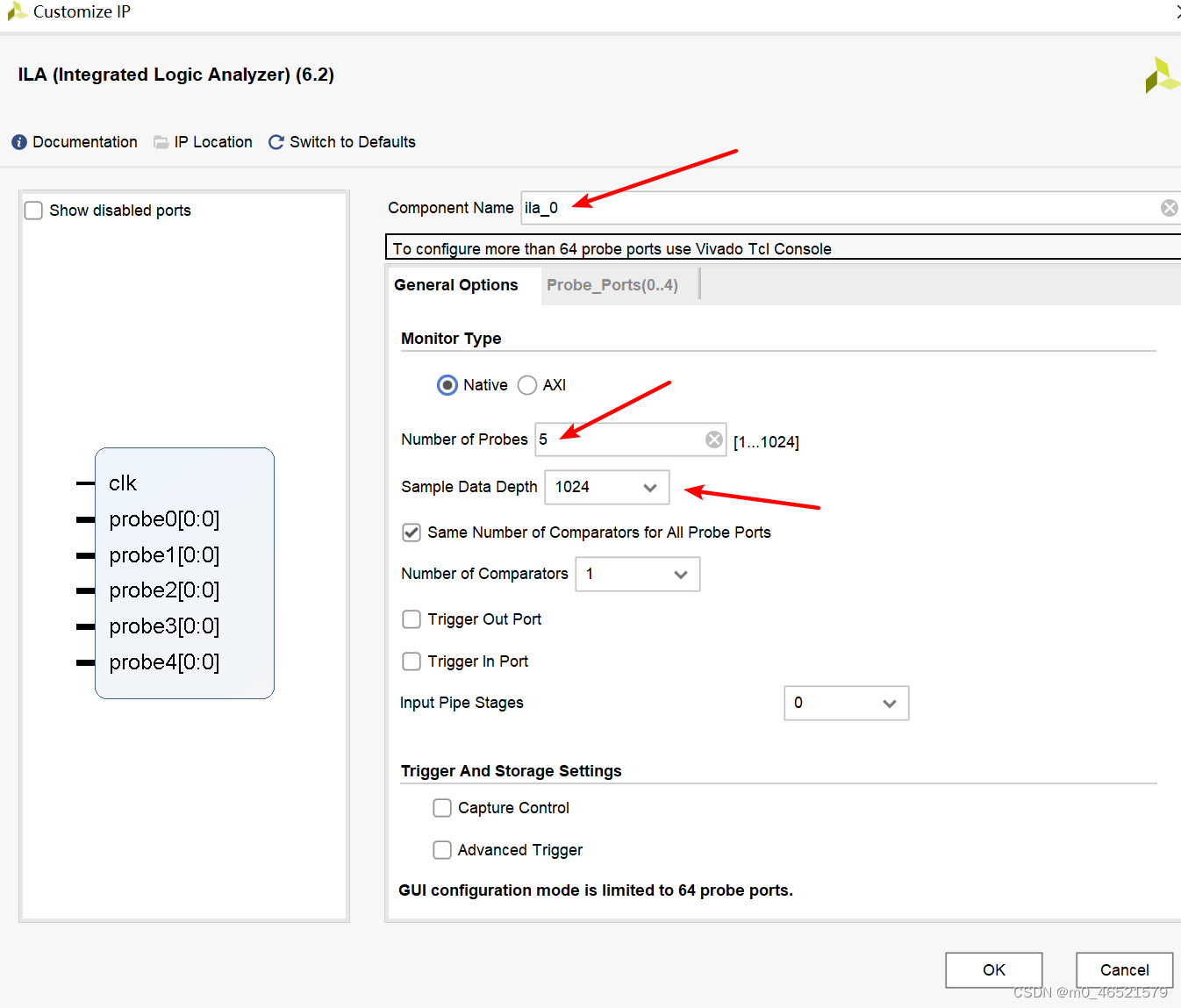

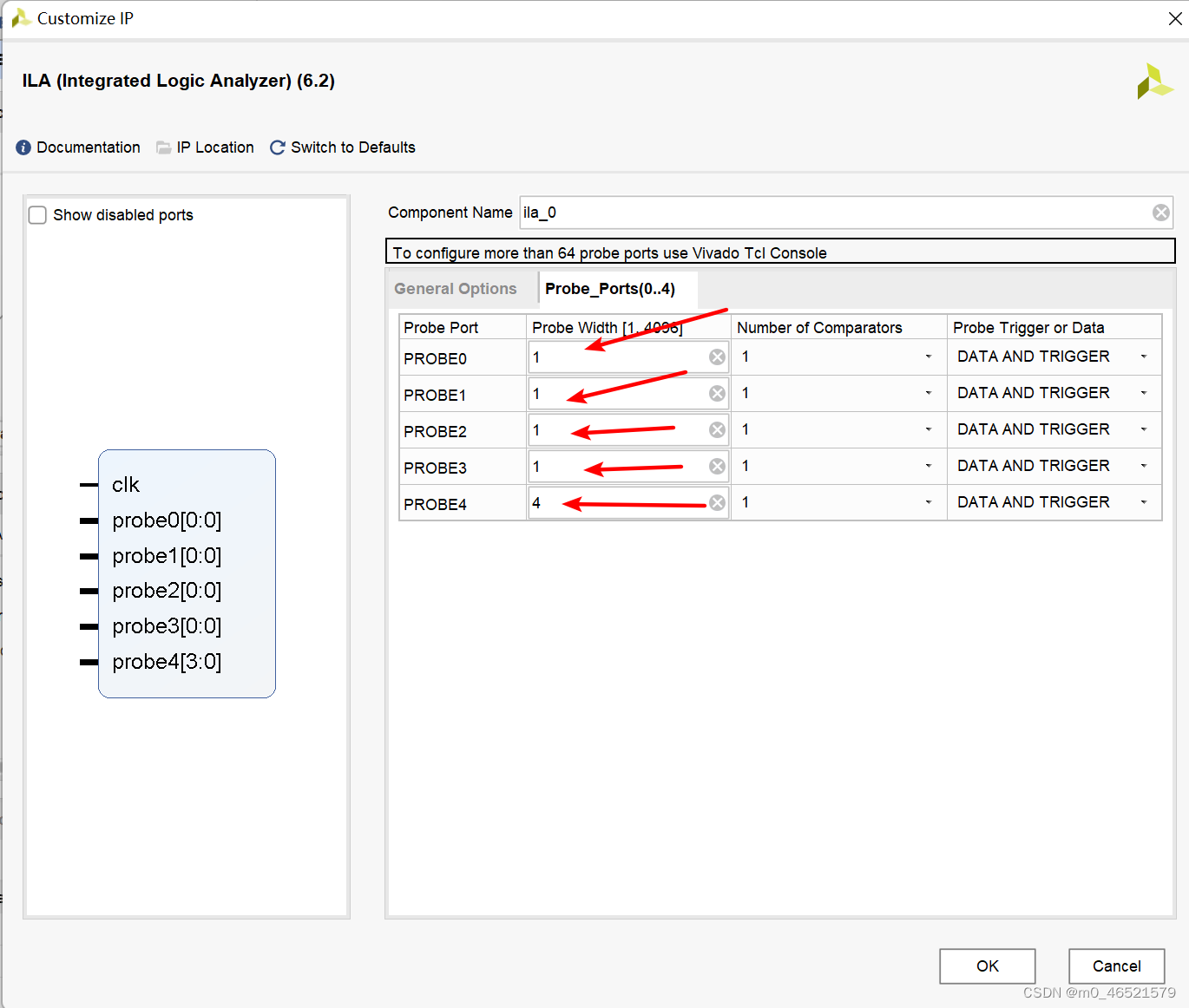

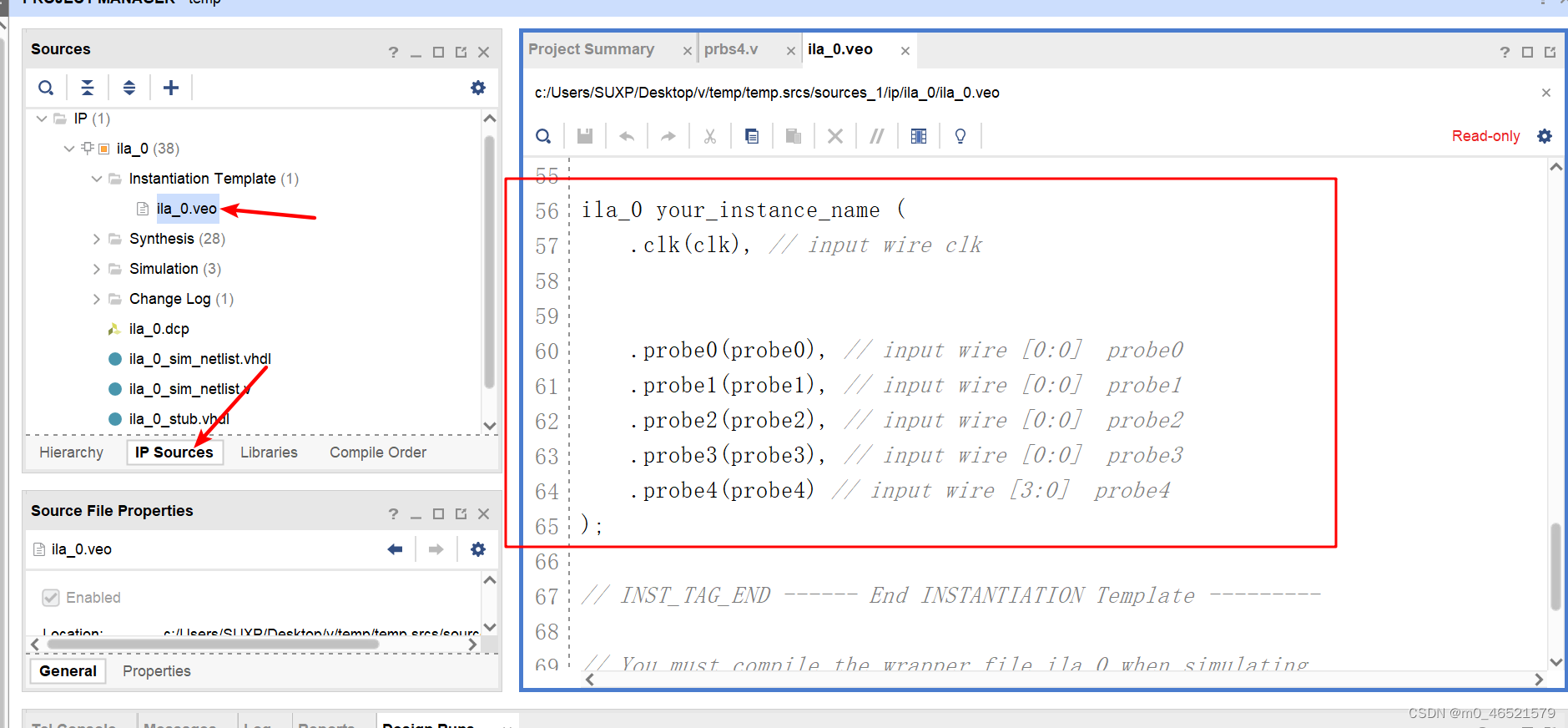

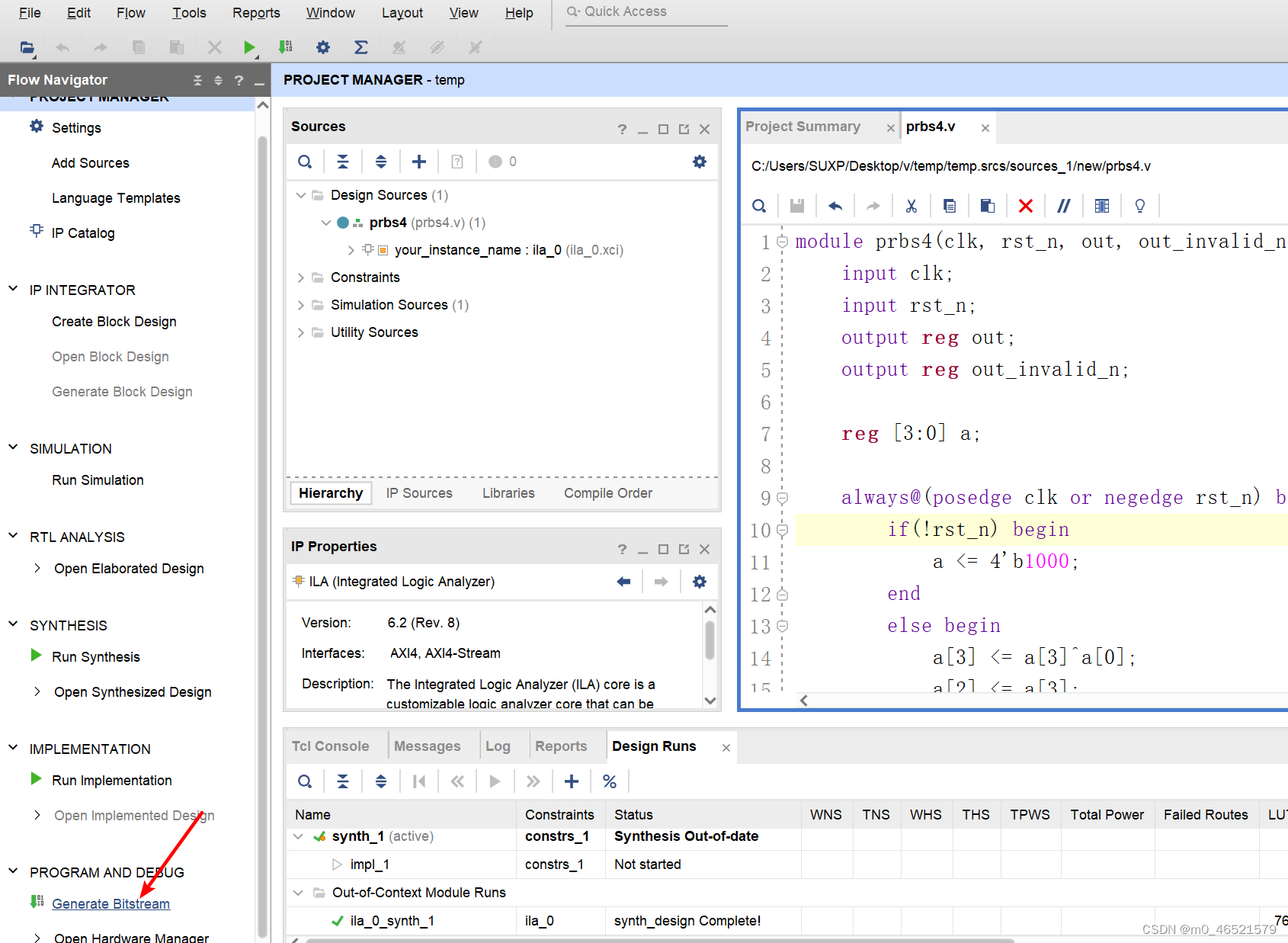

将图中的红色方框中的模板代码复制并粘贴到顶层 HDL 代码中,并将 ILA 的时钟和探针信号连接到顶层设计中,例化 ILA IP 核的代码如下:

module prbs4(clk, rst_n, out, out_invalid_n); input clk; input rst_n; output reg out; output reg out_invalid_n; reg [3:0] a; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin a <= 4'b1000; end else begin a[3] <= a[3]^a[0]; a[2] <= a[3]; a[1] <= a[2]; a[0] <= a[1]; end end always@(posedge clk or negedge rst_n) begin if(!rst_n) begin out <= 1'b0; out_invalid_n <= 1'b0; end else begin out <= a[0]; out_invalid_n <= 1'b1; end end ila_0 your_instance_name ( .clk(clk), // input wire clk .probe0(clk), // input wire [0:0] probe0 .probe1(rst_n), // input wire [0:0] probe1 .probe2(out), // input wire [0:0] probe2 .probe3(out_invalid_n), // input wire [0:0] probe3 .probe4(a) // input wire [3:0] probe4 ); endmodule讯享网

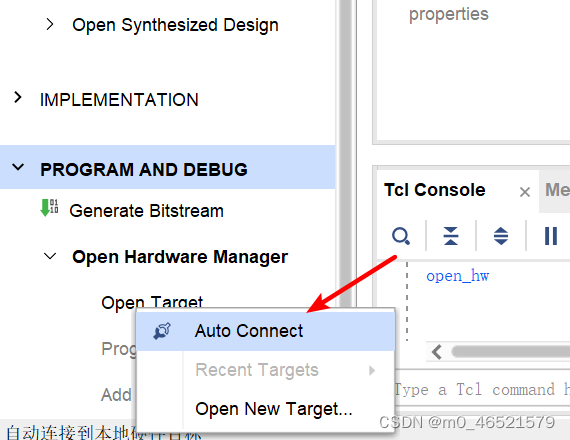

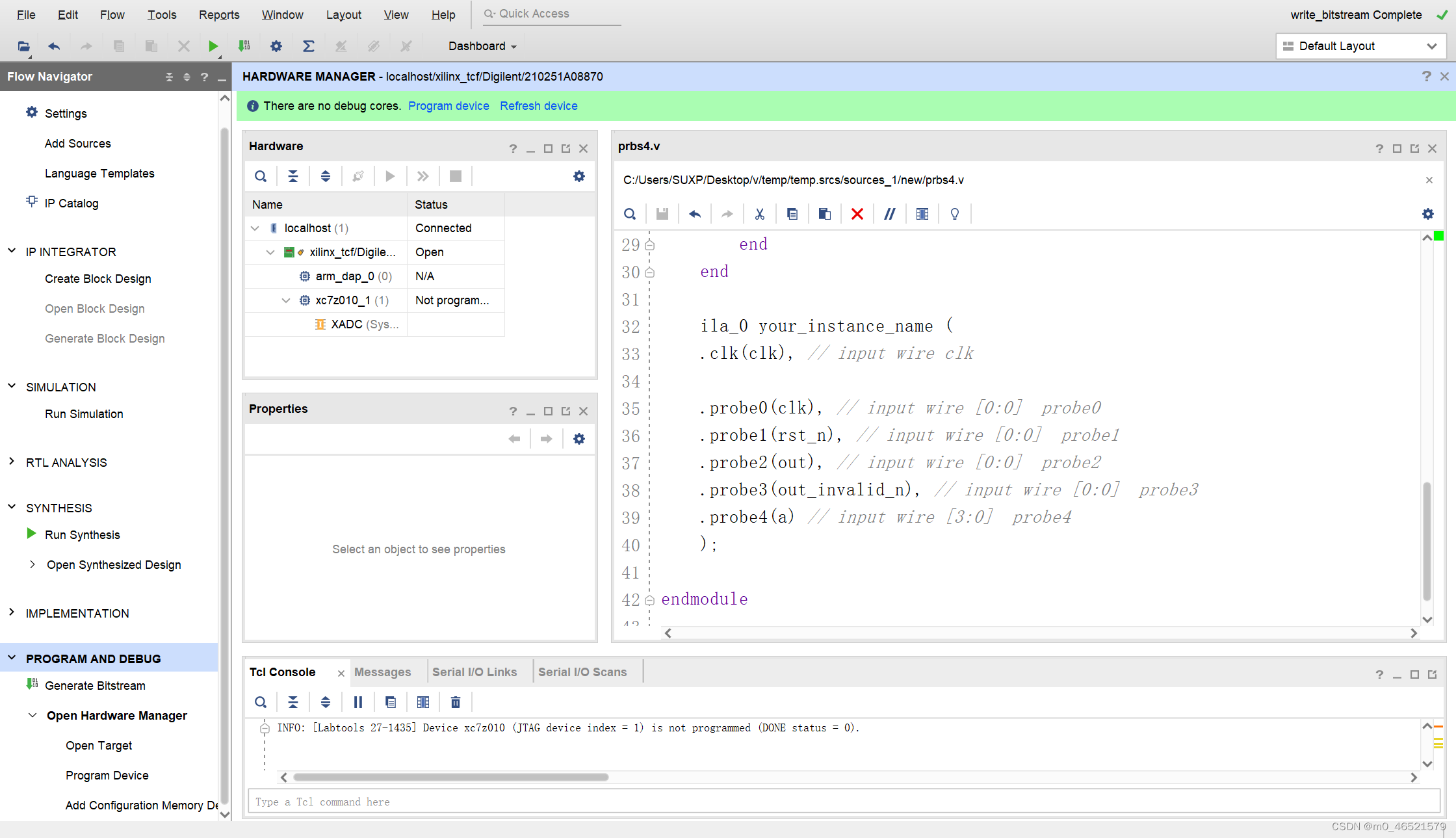

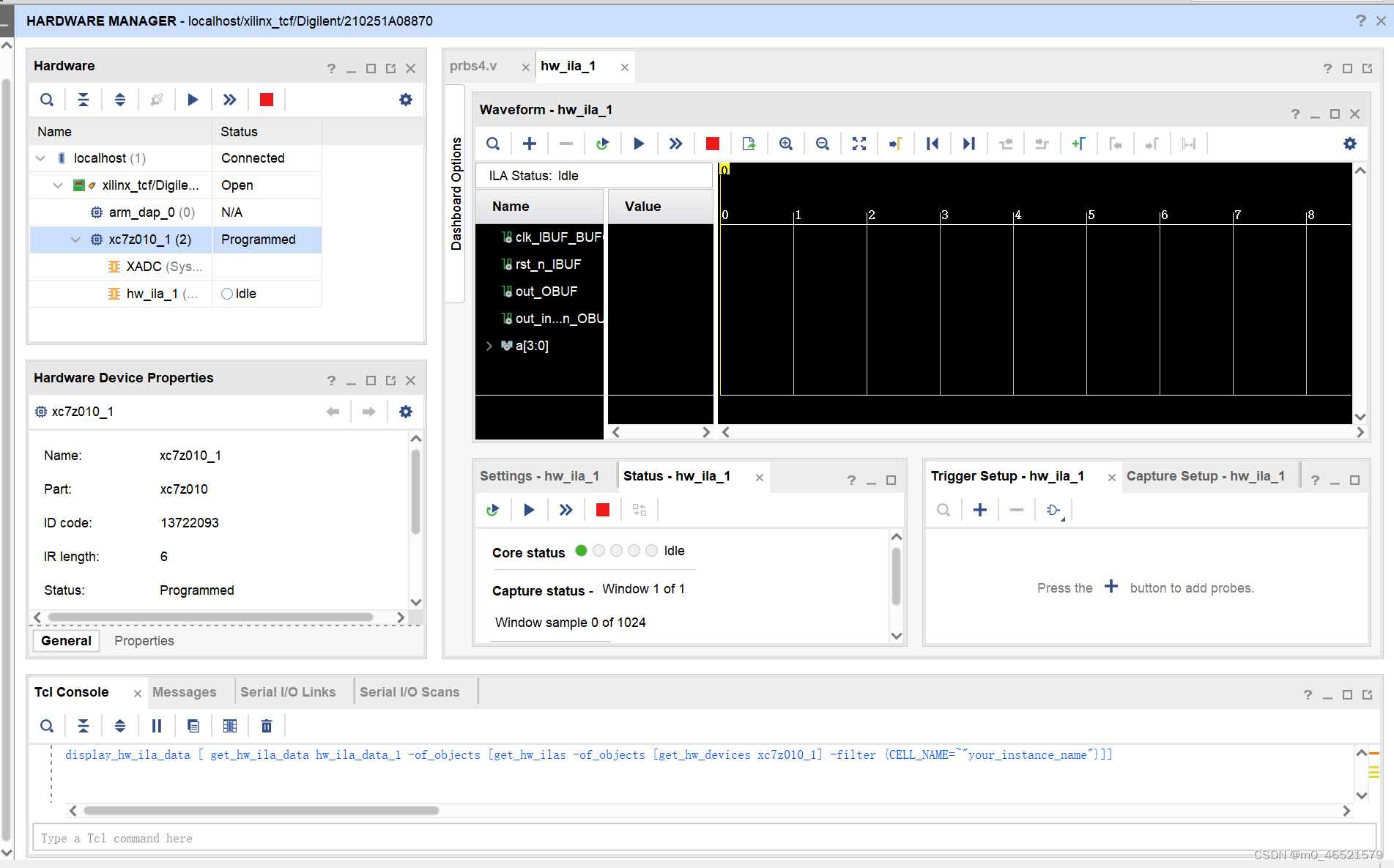

连接开发板

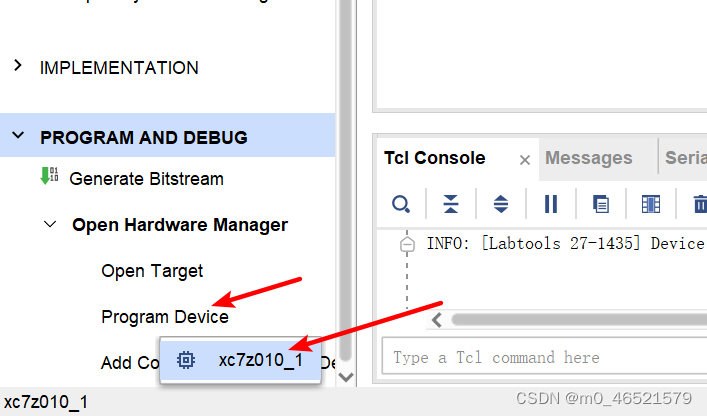

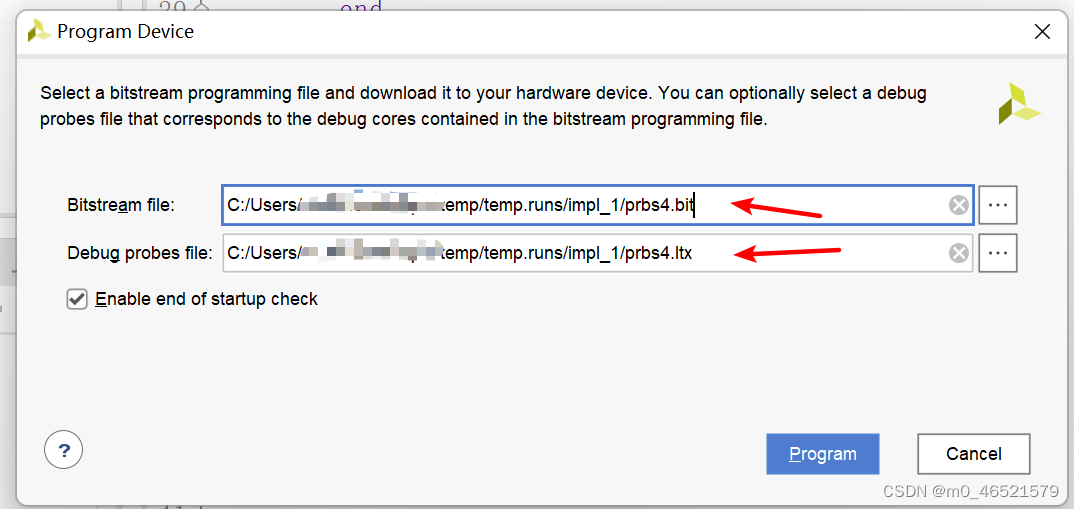

.ltx文件存储了调试探针的信息,用来传递给Vivado IDE,它是从我们的设计中被提取出来的。通常,调试探测文件是在实现过程中自动创建的,并位于和比特流文件相同的目录下。若实现后的设计中包含了ILA IP核,则在下载比特流时,Vivado会自动识别出.ltx 文件。这里我们不必太多地关注此文件,只要按照 Vivado 自动的设定来下载设计即可。

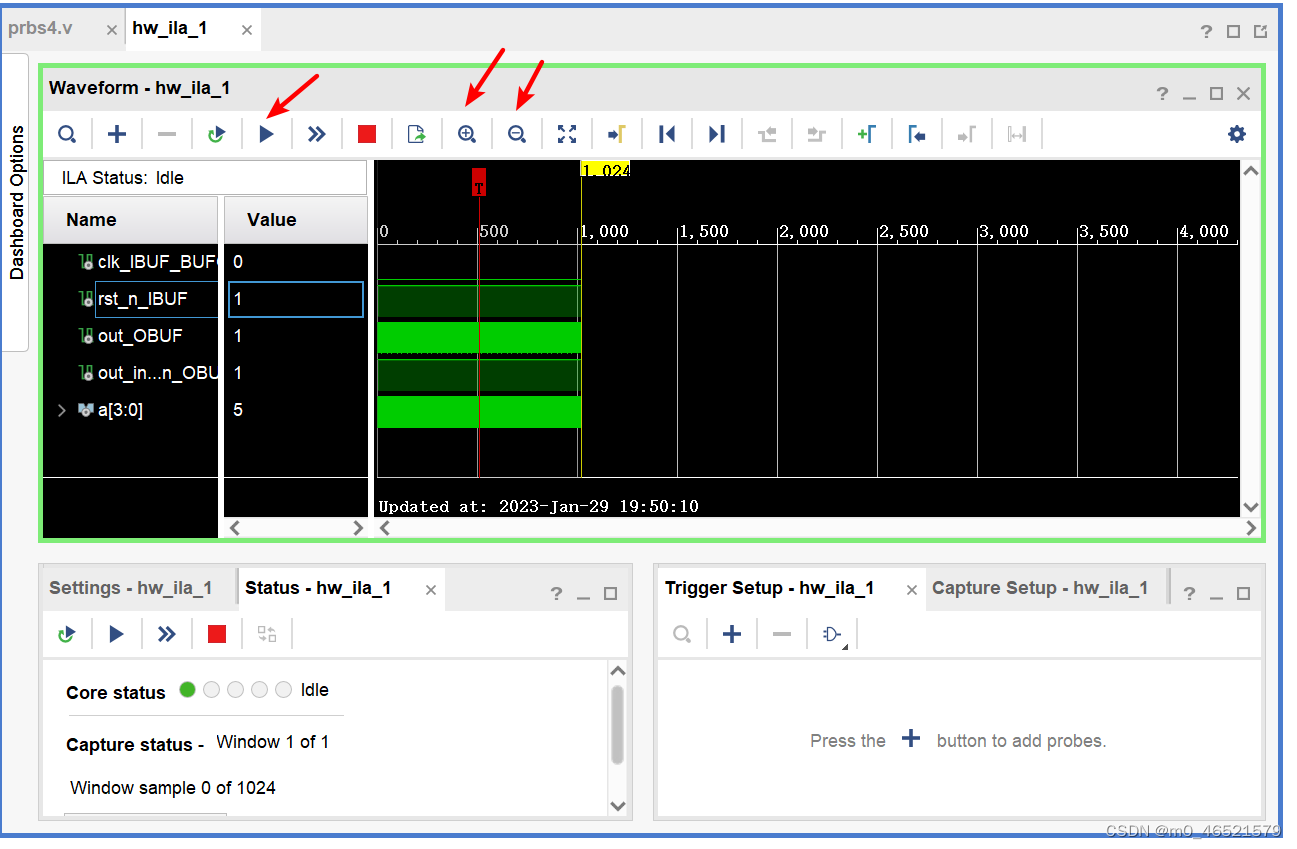

点击Program,

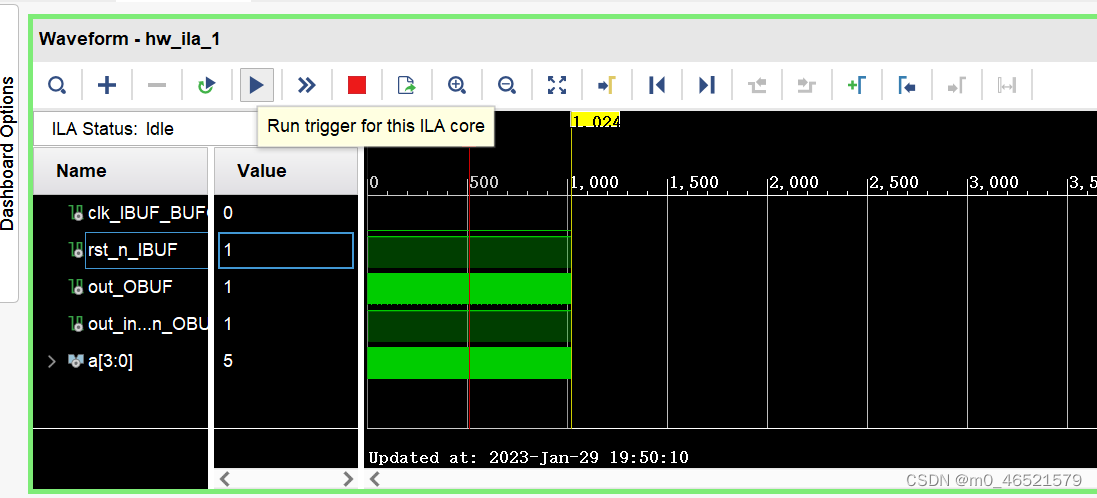

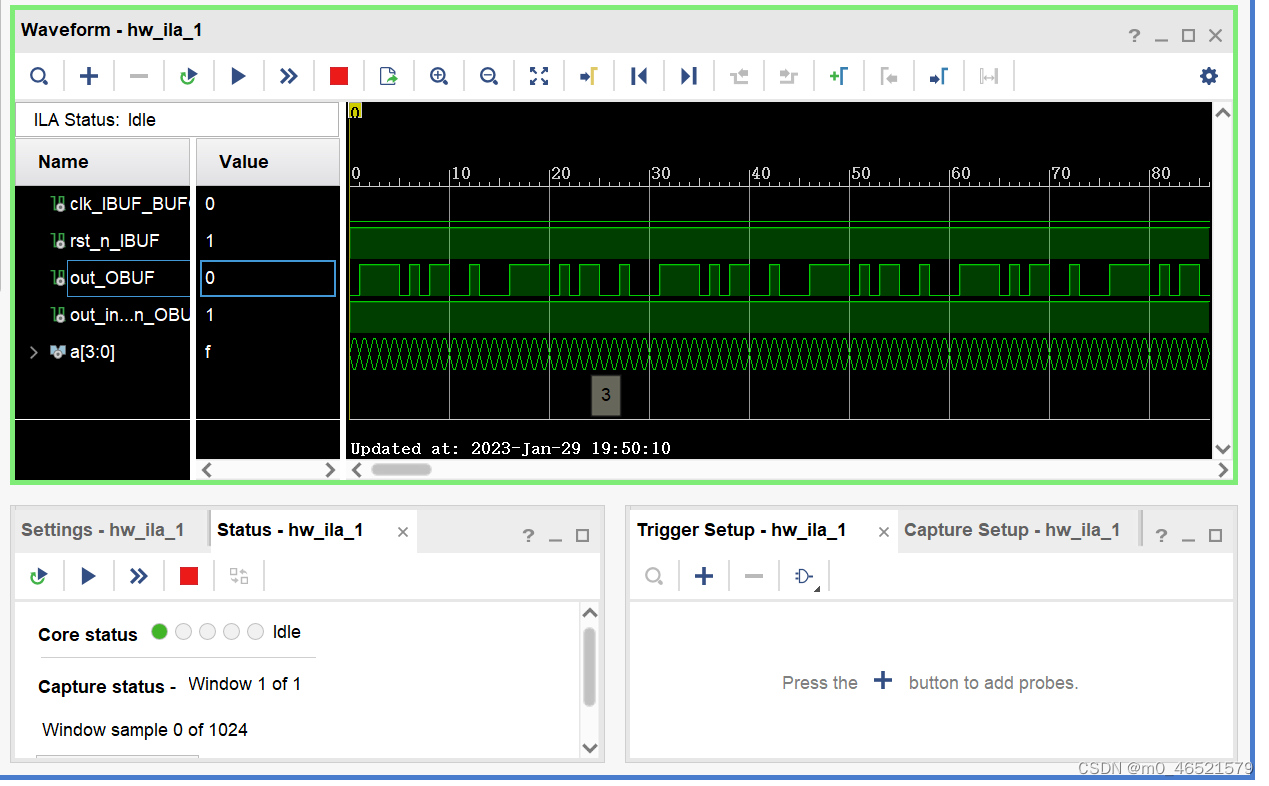

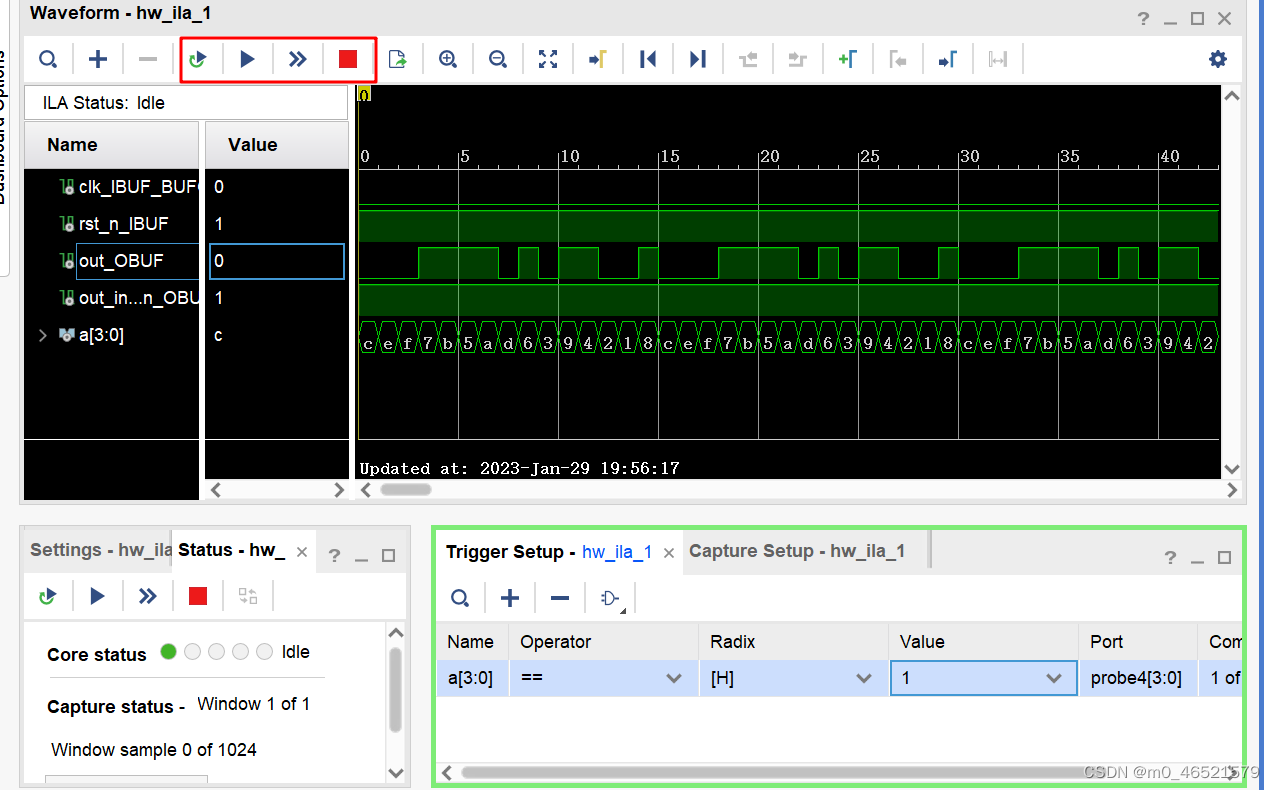

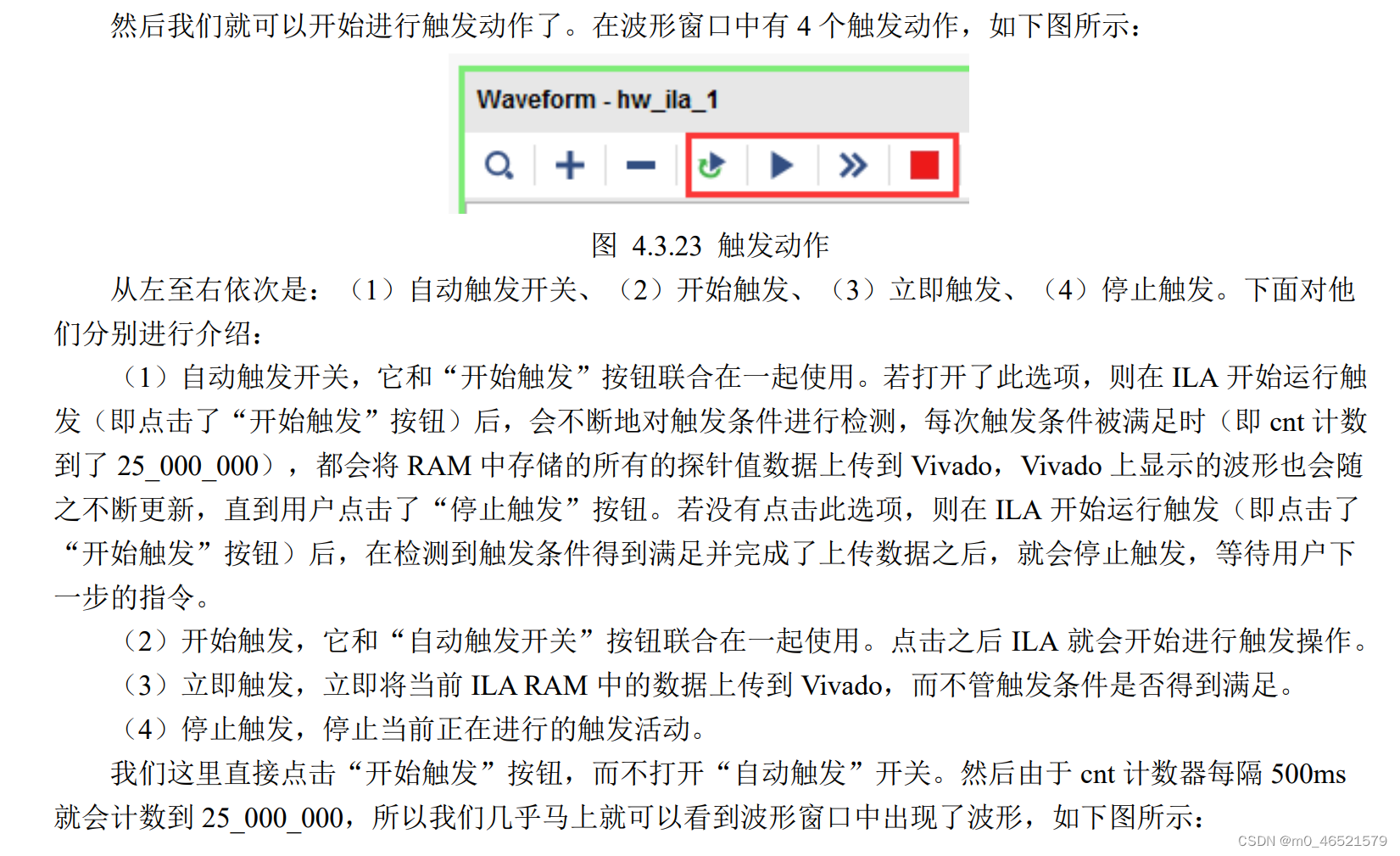

触发就是决定 ILA 会在什么时候 将 RAM 中的探针值数据上传到 Vivado,当 ILA 检测到触发条件得到满足时,就会把 RAM 中的探针值数据 上载到 Vivado,然后 Vivado 将探针数据的波形显示出来。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/46177.html