- zynq开发流程如下所示,其中在SDK属于软件层面开发

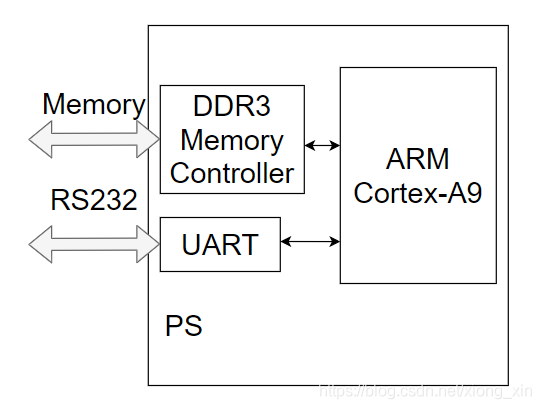

讯享网 - zynq开发最小系统,ps指zynq里的ps部分,核心为ARM Cortex A9处理器。周围两个外设,DDR3内存控制器用于存储数据,UART用于与外界通信

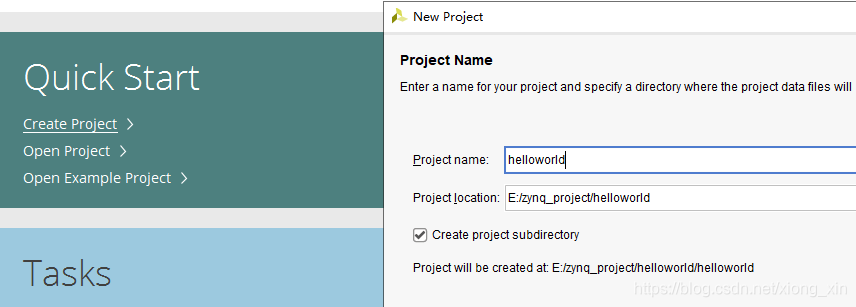

- 打开vivado新建工程,工程名为英文,路径也为英文可包含下划线

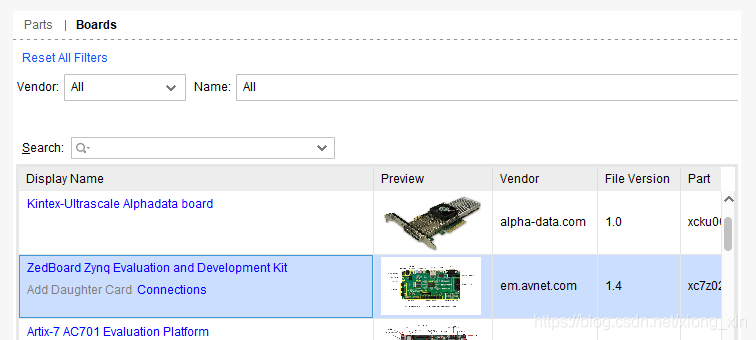

- 一路next,有芯片的选芯片型号,有板子的直接选用板子然后finish

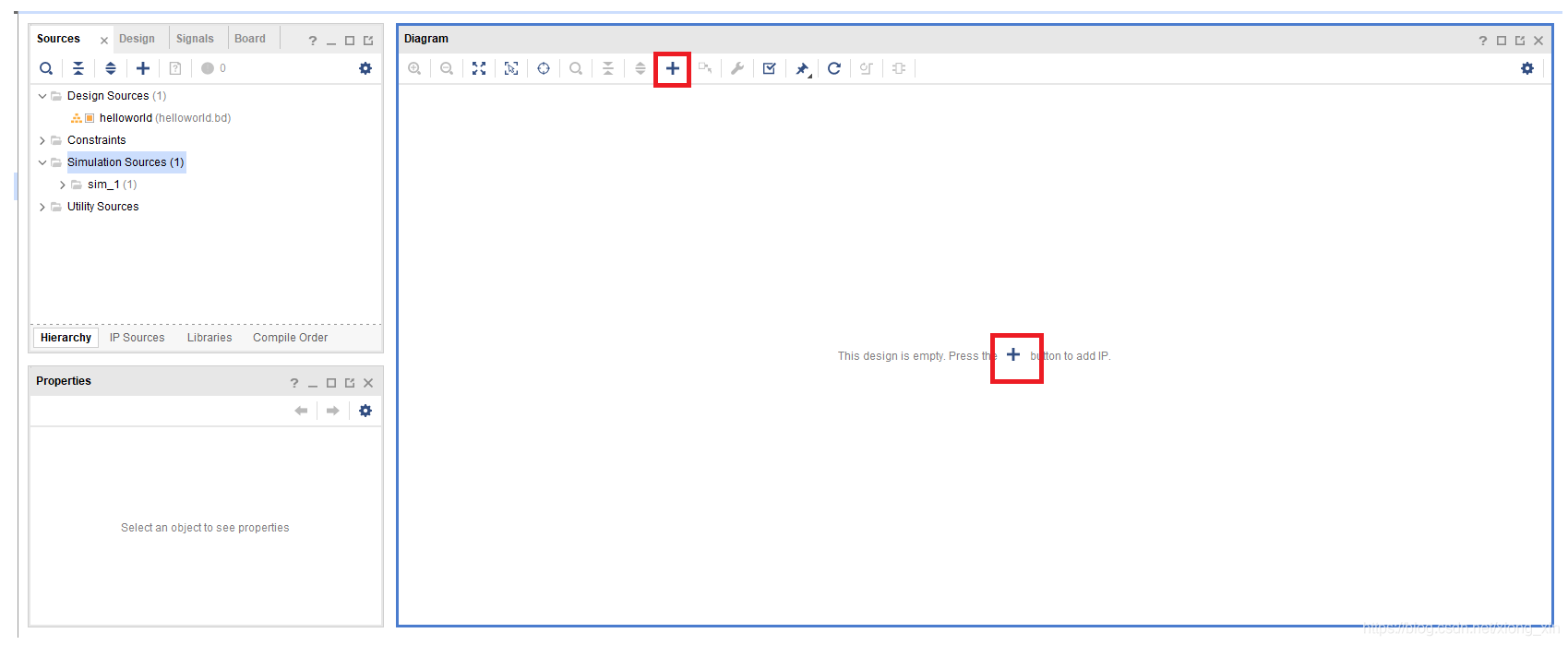

- 模块化设计点击Create block design

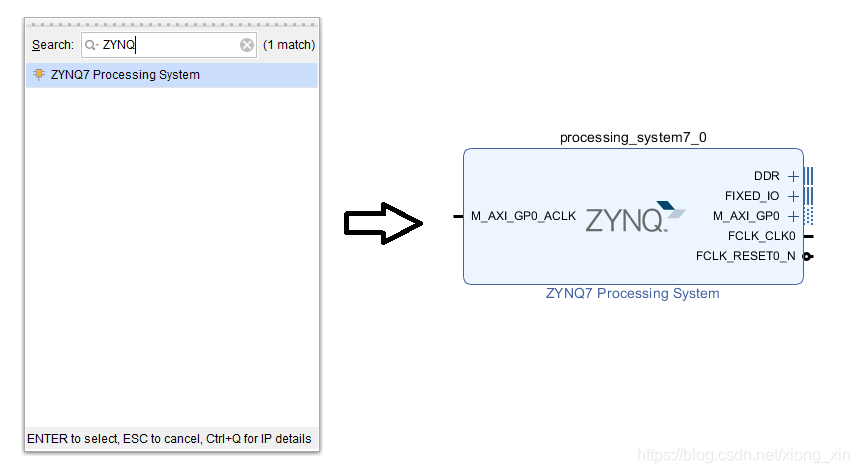

- Diagram下点击加号新建IP

- 输入zynq按下enter表示选中该模块,经过一段时间后vivado自动生成好了

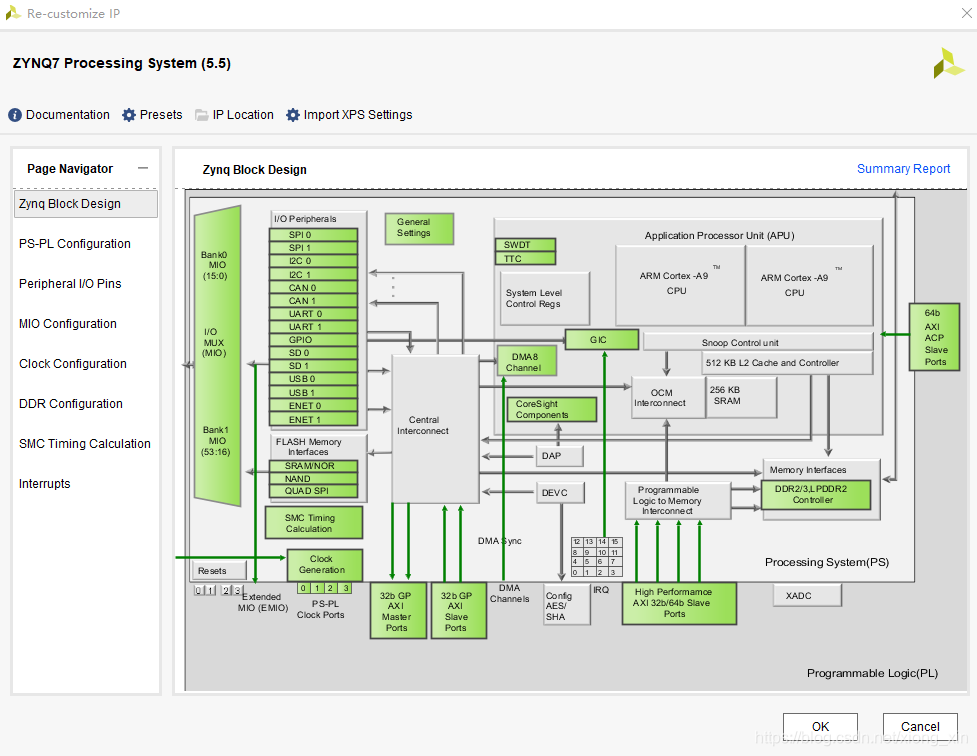

- 双击IP核对它进行配置,打开页面如下图所示。方框里面是PS,方框外面是PL。

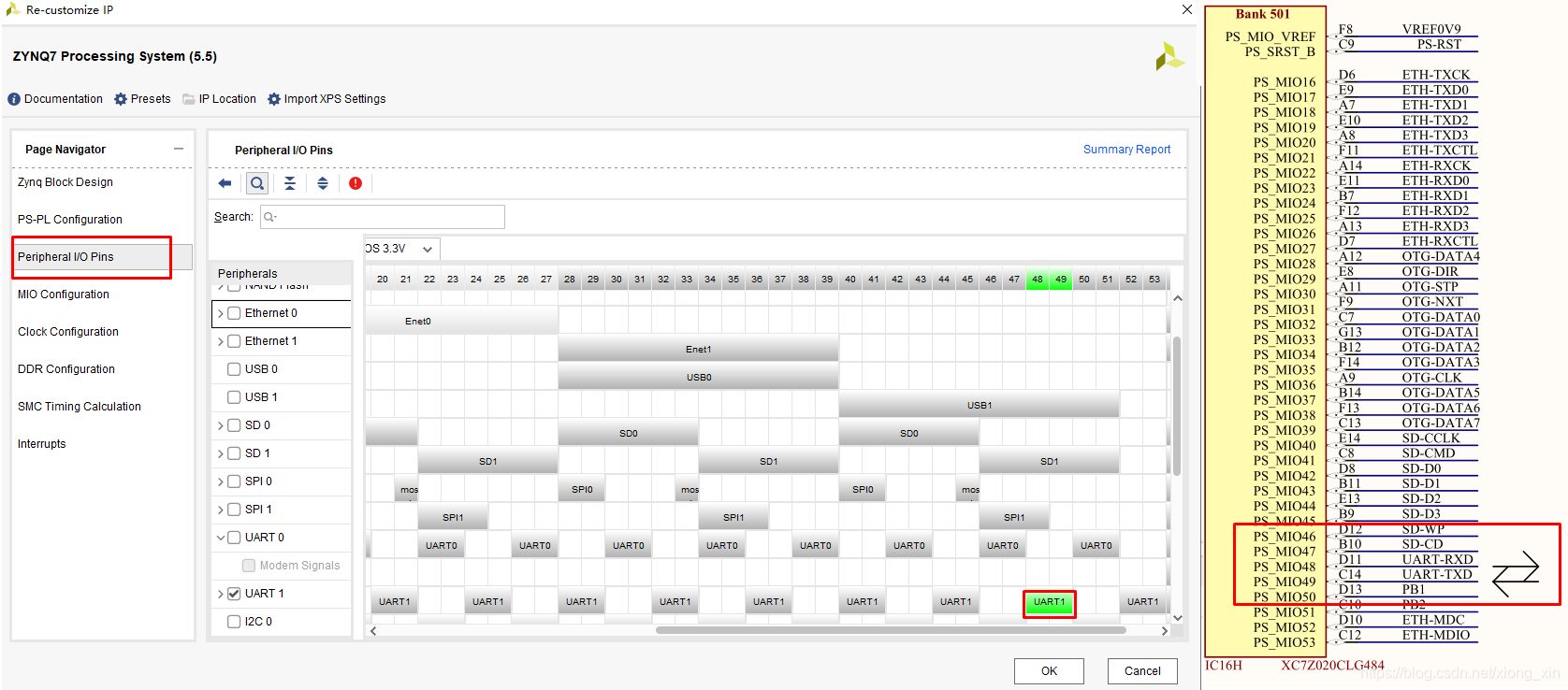

- 根据Zedboard原理图Bank501UART对应的MIO4849选择Peripherla I/O Pins勾选一个UART1对应4849

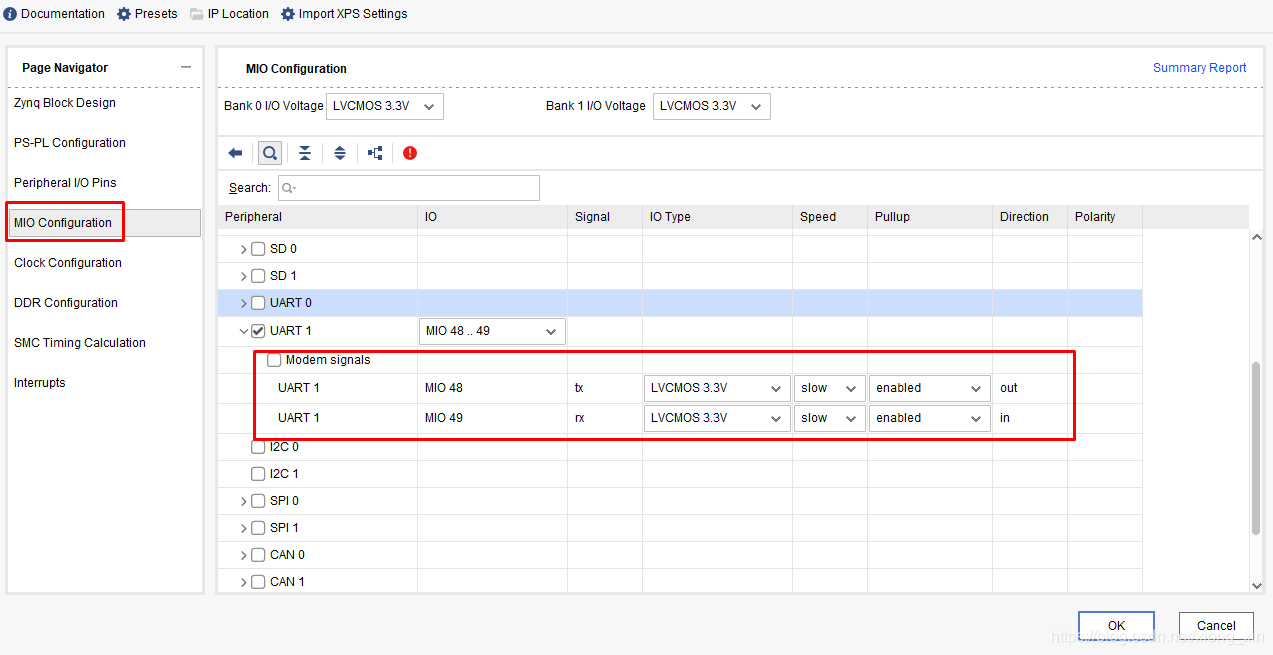

- 或者直接在MIO Configuration勾上UART1自动显示MIO4849,48对应tx,49对应rx这与原理图是一致的

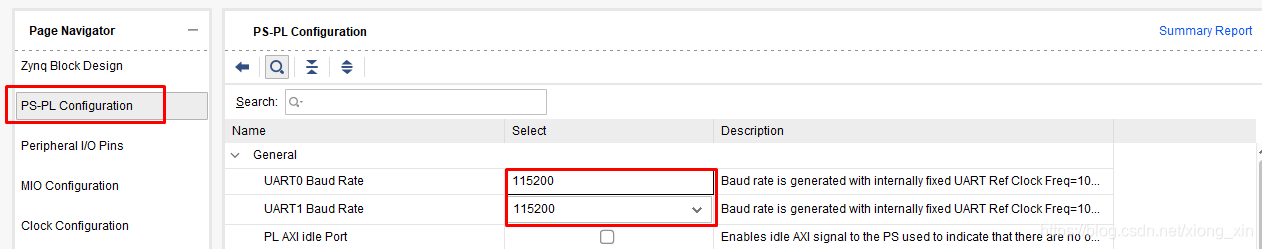

- 配置UART波特率为

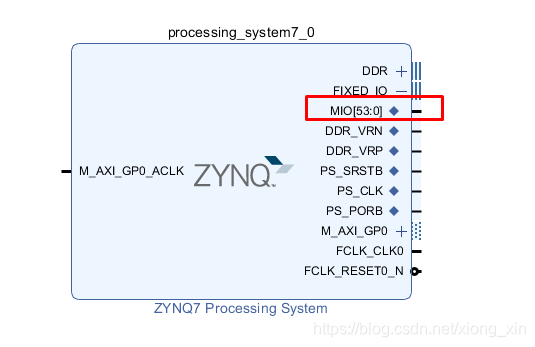

- 配置完UART原理图没有任何变化,因为UART属于FIXED_IO,展开FIXED_IO,UART属于MIO[53:0]

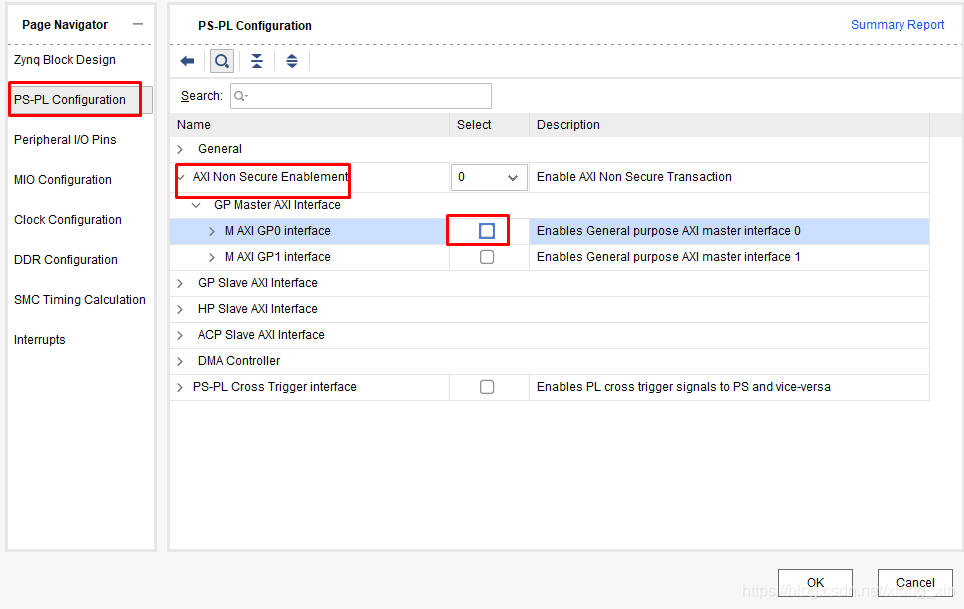

- 删除M_AX_GP0接口,这属于PS和PL间接口,点击PS-PLConfiguration点击第二个,展开把 M AXI GP0 interface前的勾去掉

- 顺便也删了M_AX_GP0_ACLK接口,这是M_AX_GP0附带的时钟信号

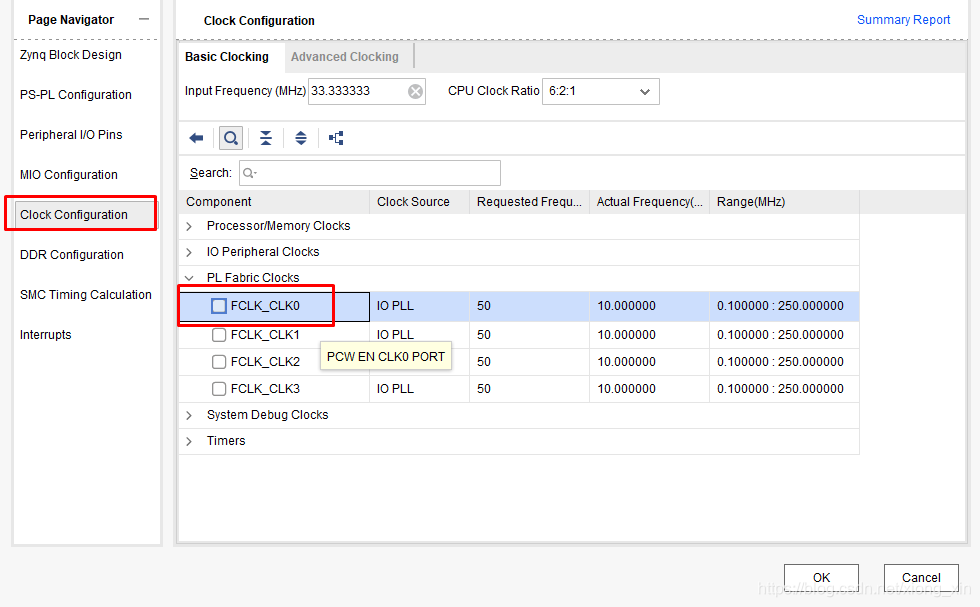

- FCLK_CLK0是PS提供给PL的时钟信号,在时钟端点击Clock Configuration展开PL Fabric Clocks把FCLK_CLK0前的勾取消掉

- 时钟取消掉的原理图如下图所示

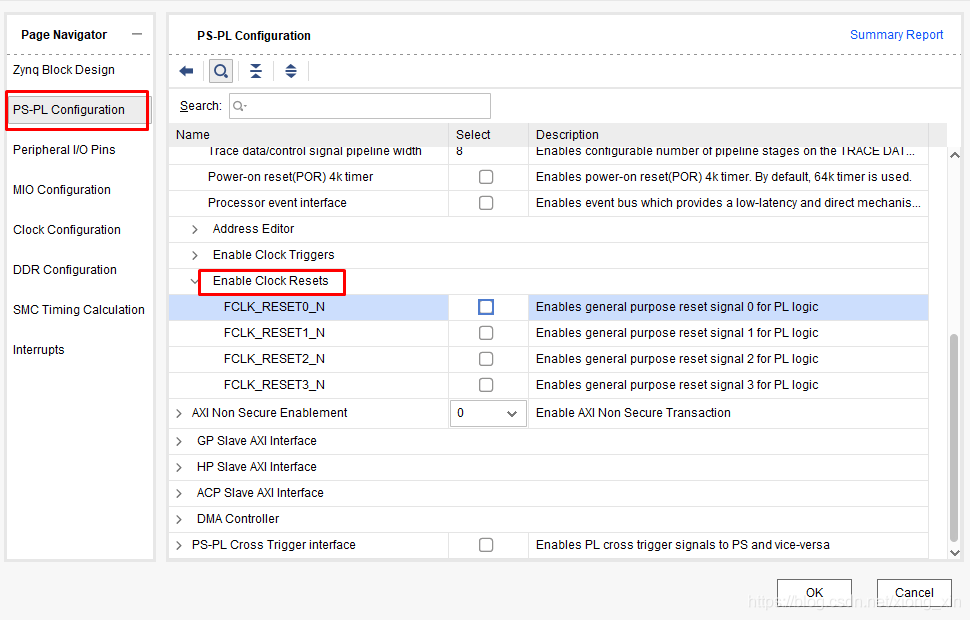

- FCLK_RESET0_N是PS提供给PL的复位接口,在PS-PL Configuration点击General,展开Enable Clock Resets,把FCLK_RESET0_N前的勾取消掉

- zynq上不用的接口完全被移除掉了

- 点击接口右键make external(run block automation也可以帮忙完成端口创建)

- 扩展出来的端口可以连接到器件引脚上

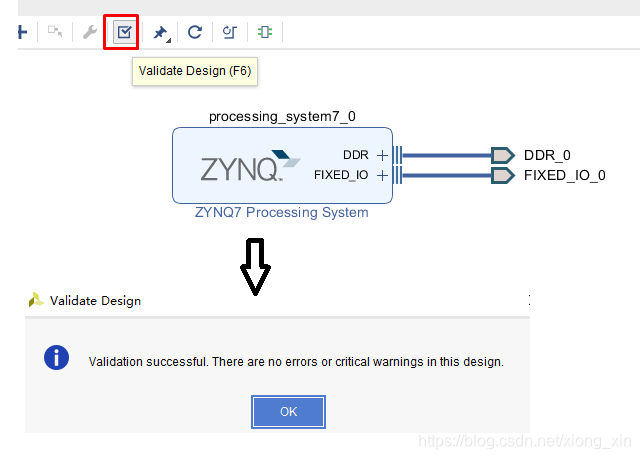

- 可以点击validate design来验证结果有没有问题

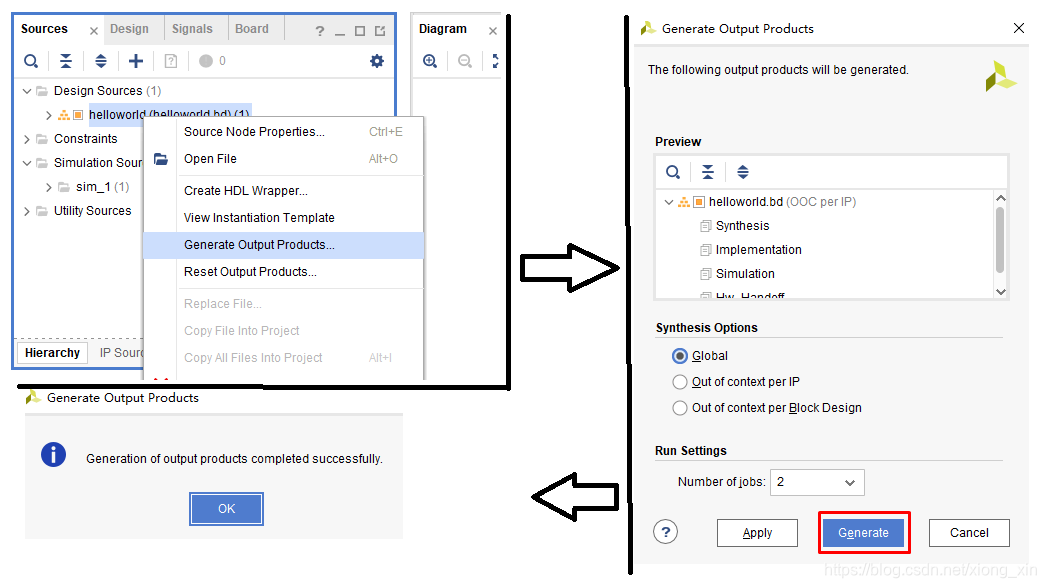

- 在sources下右击bd文件Generate Output Products可勾选global或直接点击Generate

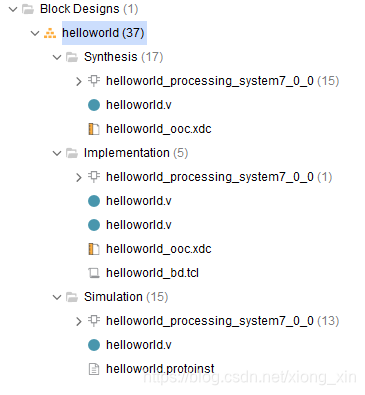

- 生成结果可以点击IP Sources查看,可以看出生成了管脚约束,ps端不需要另外管脚约束在这就已经自动生成了

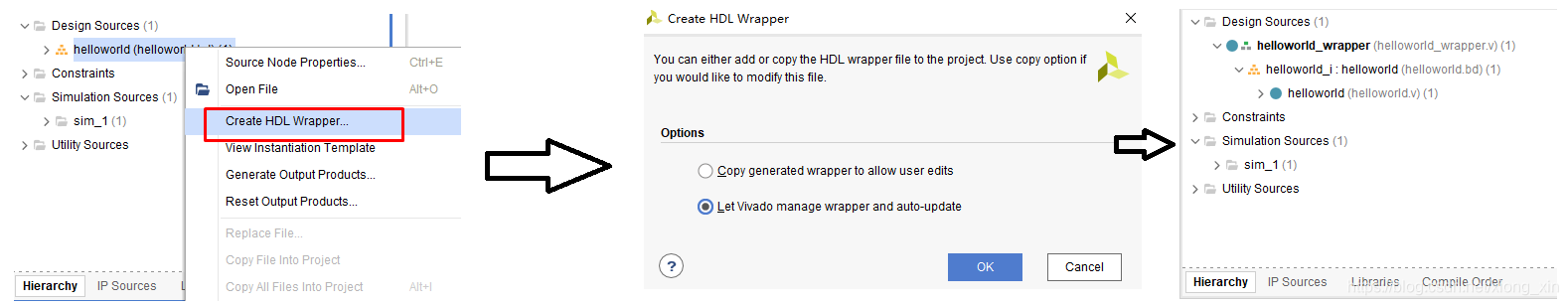

- 返回Hierarchy,右键点击Create HDL Wrapper生成顶层文件。保持默认让vivado管理自动更新,点击OK

- 可以看到多了一个_wrapper.v的顶层文件,文件里有DDR和FIXED_IO的端口声明

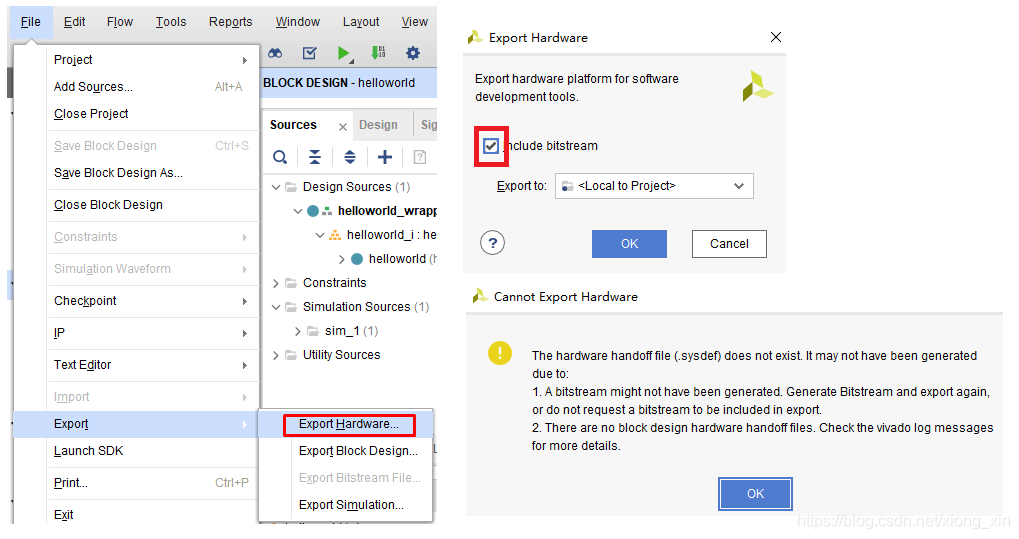

- 导出硬件到SDK,没有设计到PL部分的开发所以不需要include bitstream,勾不需要勾,不然弹出黄色警告

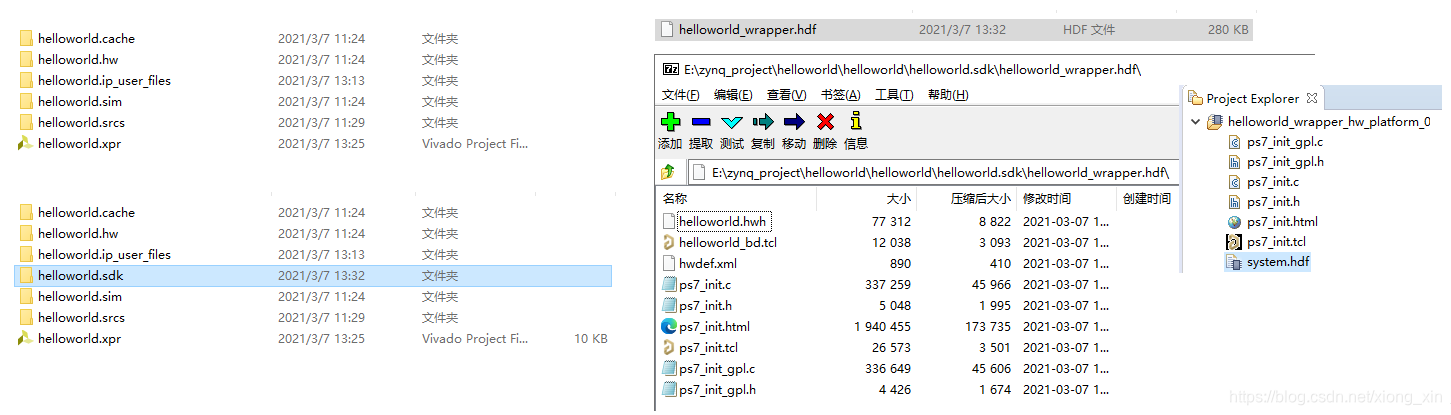

- 导出硬件后可以看出多了一个sdk文件夹,里面只有一个hdf文件,这是一个压缩文件可以直接打开来看,导入sdk后加载的文件

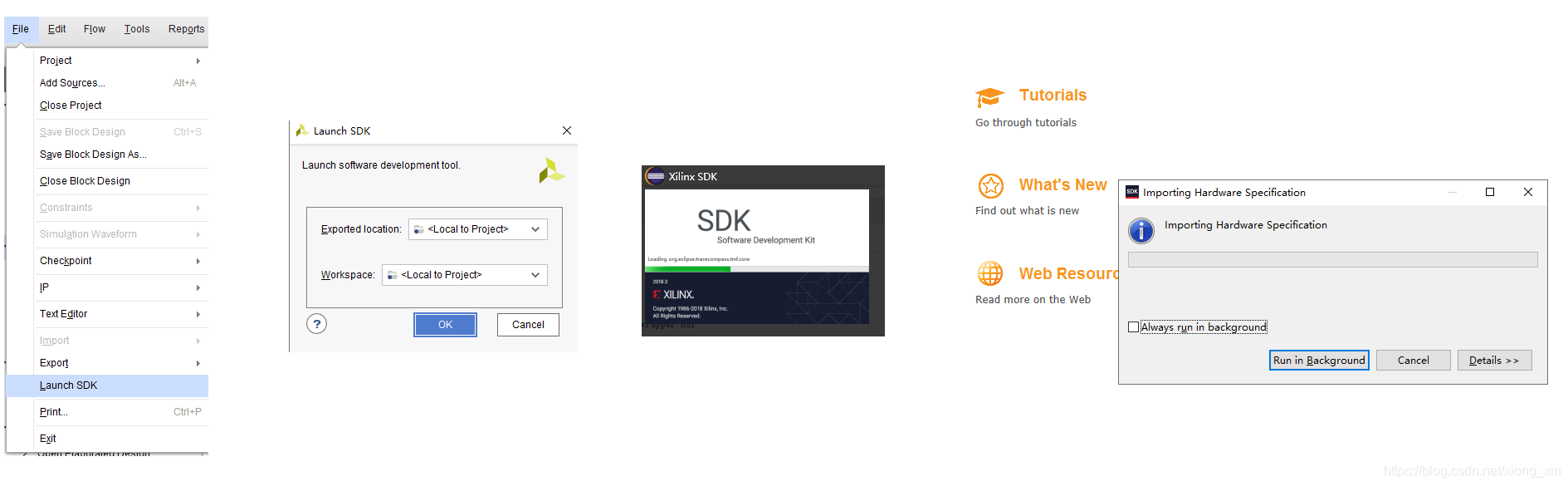

- 然后点击下一个选项,launch sdk点击OK可以看见SDK在加载中

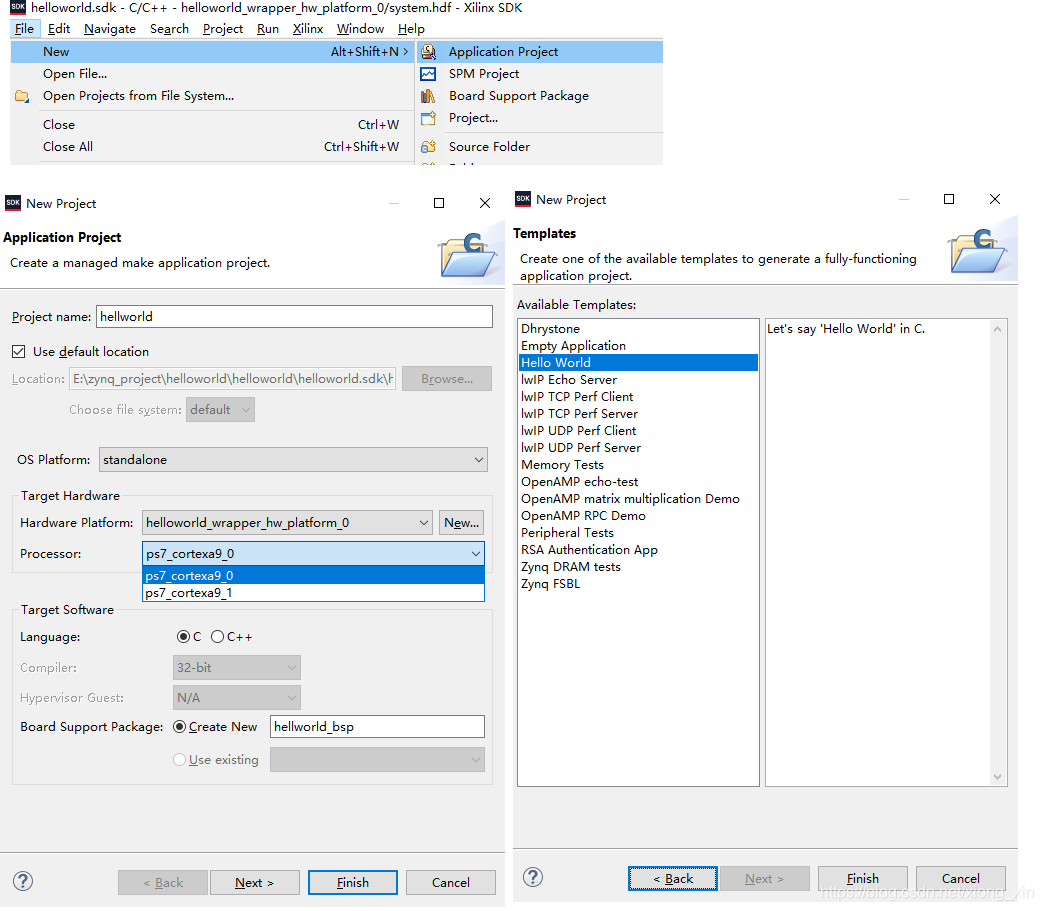

- 新建一个application project,Processor下拉有两个说明这是一个双核处理器,保持默认即可,选择模板Hello world后Finish,也可以直接从空模板开始敲

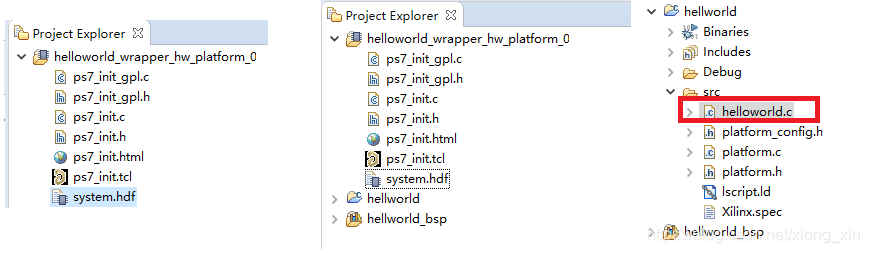

- 可以看出生成了一个helloworld工程,helloworld_bsp是板级支持包,展开src,里的helloworld.c是主文件

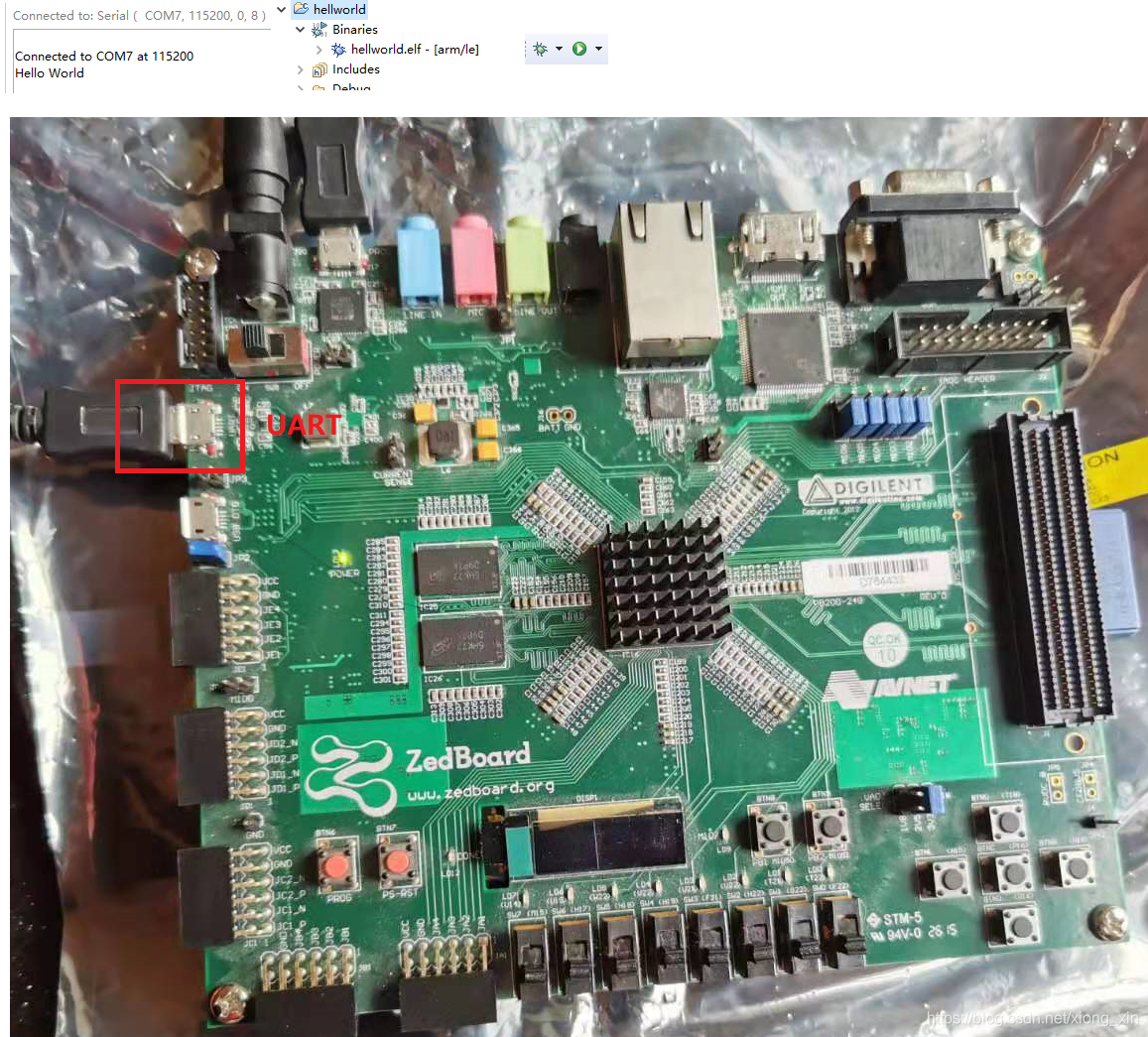

- 打开SDK Terminal点击加号新建串口,Port选择com 7(根据设备管理器确定)后OK

- 没有对PL部分进行编程故直接点绿色三角开始运行即可,将elf文件下载进板子(elf是arm上的可执行文件),可以看见SDK的串口打印出Hello World,这是可执行文件输出的字符串通过串口发送给电脑

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/44834.html