--ujs-lili library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_unsigned.ALL; use IEEE.STD_LOGIC_arith.ALL; entity shijinzhi is port(clk,rst,en:in std_logic; cq:out std_logic_vector(3 downto 0); cout:out std_logic); end shijinzhi; architecture Behavioral of shijinzhi is signal cq1: std_logic_vector(3 downto 0):="0000"; begin process(clk,en,rst) begin if rst='1' then cq<="0000";cout<='0'; elsif clk'event and clk='1' then if en='1' then if cq1<"1001" then cq1<=cq1+'1'; cout<='0'; else cq1<="0000"; cout<='1'; end if; end if; end if; cq<=cq1; end process; end Behavioral; 讯享网

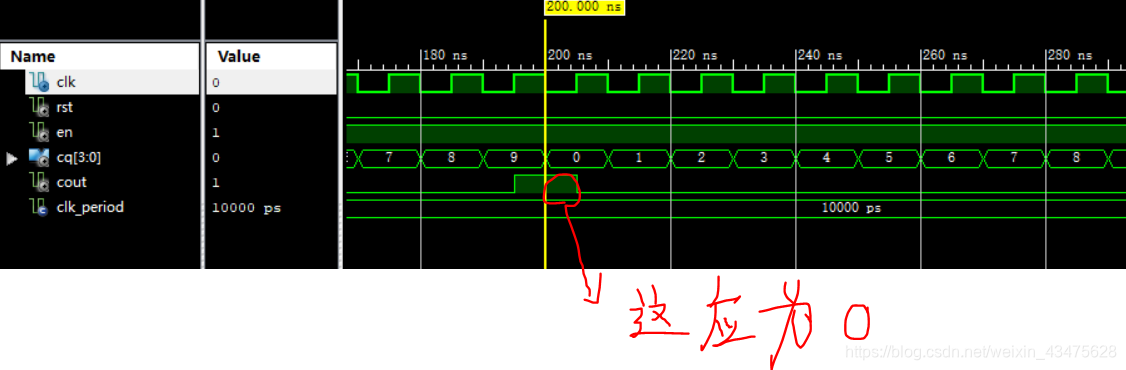

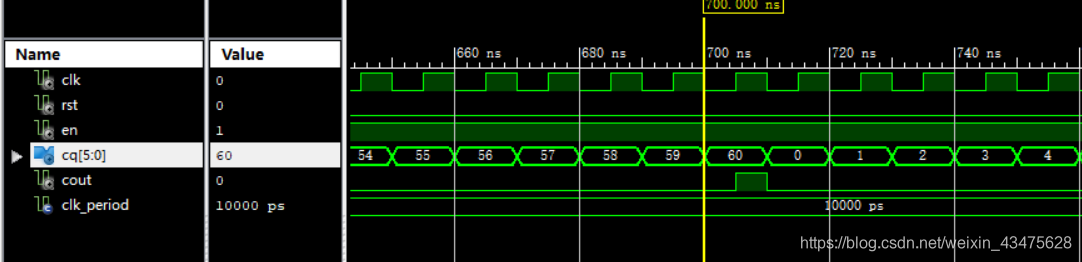

仿真会发现,cout在0的正半周期也有,这是不对的。

讯享网

那肯定是cout写的不对。而且是赋值为0的地方写的不对。

讯享网--ujs-lili library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_unsigned.ALL; use IEEE.STD_LOGIC_arith.ALL; entity shijinzhi is port(clk,rst,en:in std_logic; cq:out std_logic_vector(3 downto 0); cout:out std_logic); end shijinzhi; architecture Behavioral of shijinzhi is signal cq1: std_logic_vector(3 downto 0):="0000"; begin process(clk,en,rst) begin if rst='1' then cq<="0000";cout<='0'; elsif clk'event and clk='1' then if en='1' then if cq1<"1001" then cq1<=cq1+'1'; --改了这里 else cq1<="0000"; cout<='1'; end if; end if; end if; cq<=cq1; --改了这里 if cq1<"1001" then cout<='0'; end if; end process; end Behavioral;

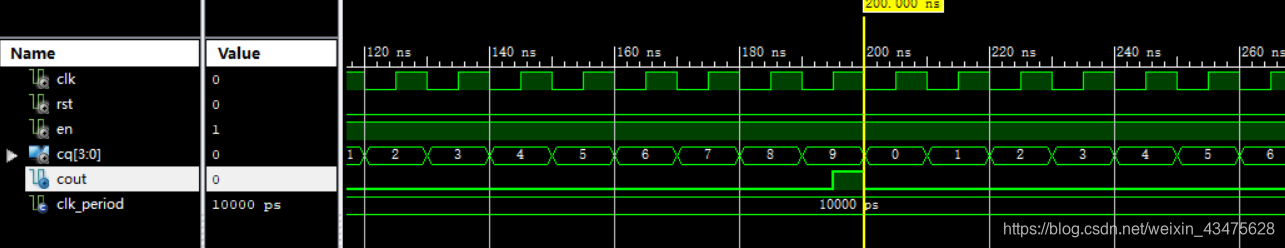

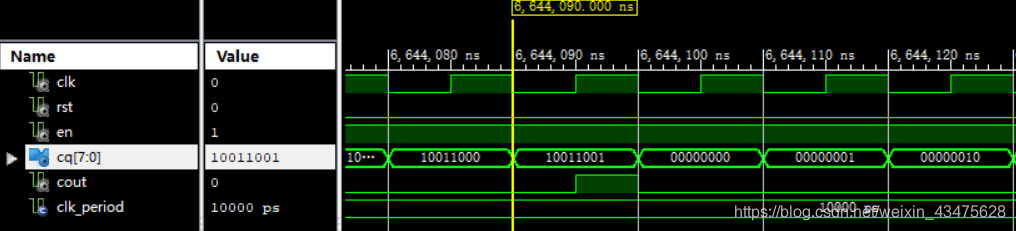

2,通过级联,两个十进制计数器做成100进制计数器

检查一下:

发现在计数到99的时候,总的进位输出为1,符合预期。

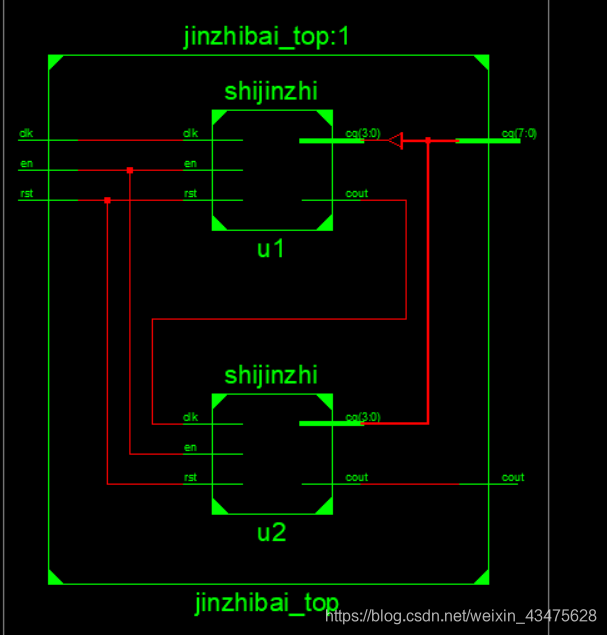

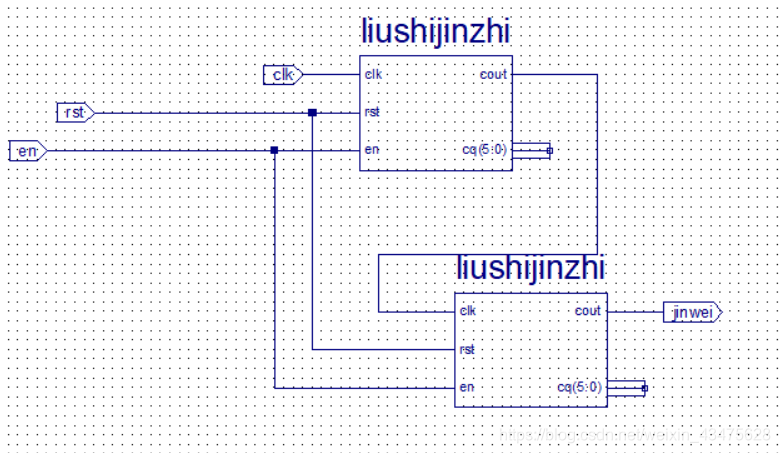

看一下元器件:

代码:

--ujs-lili library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity jinzhibai_top is port(clk,rst,en:in std_logic; cq:out std_logic_vector(7 downto 0); cout:out std_logic); end jinzhibai_top; architecture Behavioral of jinzhibai_top is component shijinzhi port(clk,rst,en:in std_logic; cq:out std_logic_vector(3 downto 0); cout:out std_logic); end component; signal a,b,c:std_logic; begin u1:shijinzhi port map(clk=>clk,en=>a,rst=>b,cq=>cq(3 downto 0),cout=>c); u2:shijinzhi port map(clk=>c,en=>a,rst=>b,cq=>cq(7 downto 4),cout=>cout); a<=en; b<=rst; end Behavioral; 下面来做一个秒到小时

这个就用16进制计数器就行了:

代码:

讯享网--ujs-lili library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_unsigned.ALL; use IEEE.STD_LOGIC_arith.ALL; entity liushijinzhi is port(clk,rst,en:in std_logic; cq:out std_logic_vector(5 downto 0);--60进制是0-59可以用range 0 to 59,也可以0011 1100 cout:out std_logic); end liushijinzhi; architecture Behavioral of liushijinzhi is signal cq1: std_logic_vector(5 downto 0):="000000"; begin process(clk,en,rst) begin if rst='1' then cq<="000000";cout<='0'; elsif clk'event and clk='1' then if en='1' then if cq1<"" then cq1<=cq1+'1'; --改了这里 else cq1<="000000"; cout<='1'; end if; end if; end if; cq<=cq1; --改了这里 if cq1<"" then cout<='0'; end if; end process; end Behavioral;

仿真:

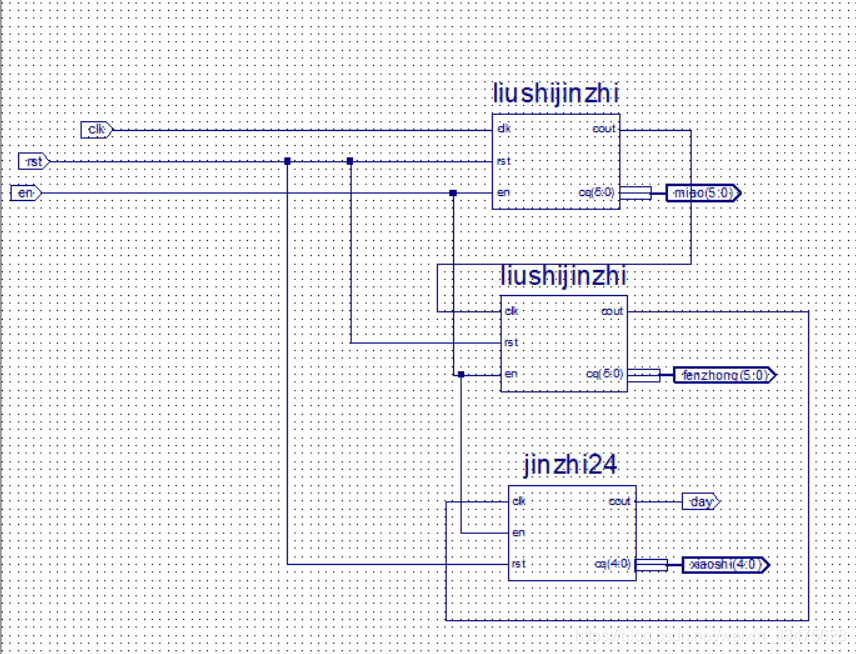

这次用硬件连接:

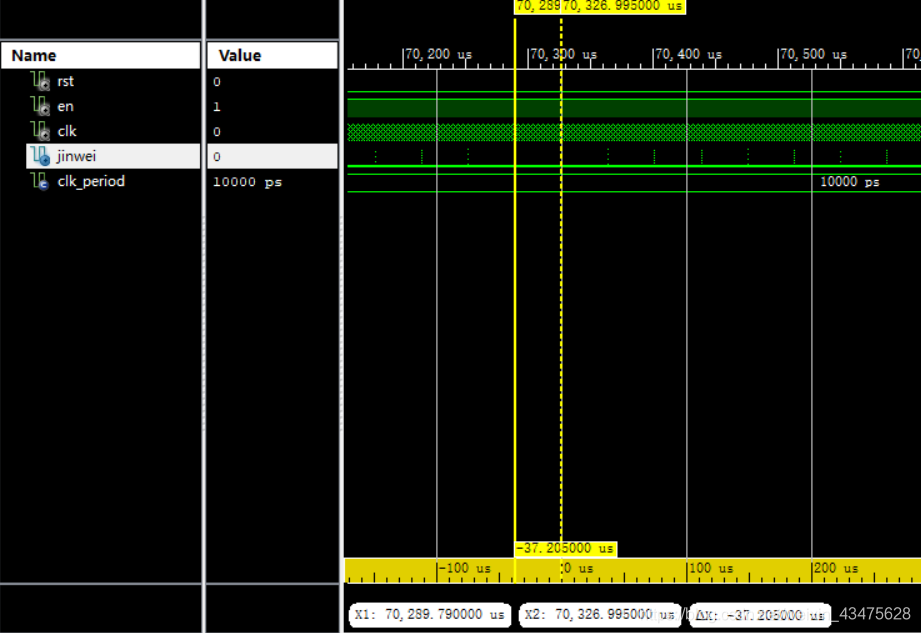

仿真:

这里的时钟周期10ns,3600*10ns=36000ns=36微秒近似等于37微秒;

仿真程序:

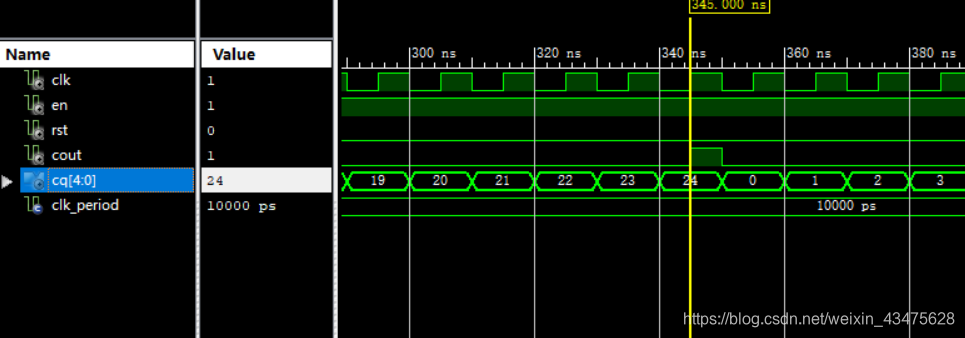

--ujs_lili LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.numeric_std.ALL; LIBRARY UNISIM; USE UNISIM.Vcomponents.ALL; ENTITY xiaoshi_top_xiaoshi_top_sch_tb IS END xiaoshi_top_xiaoshi_top_sch_tb; ARCHITECTURE behavioral OF xiaoshi_top_xiaoshi_top_sch_tb IS COMPONENT xiaoshi_top PORT( rst : IN STD_LOGIC; en : IN STD_LOGIC; clk : IN STD_LOGIC; jinwei : OUT STD_LOGIC); END COMPONENT; SIGNAL rst : STD_LOGIC; SIGNAL en : STD_LOGIC; SIGNAL clk : STD_LOGIC; SIGNAL jinwei : STD_LOGIC; constant clk_period : time := 10 ns; BEGIN UUT: xiaoshi_top PORT MAP( rst => rst, en => en, clk => clk, jinwei => jinwei ); clk_process :process begin clk <= '0'; wait for clk_period/2; clk <= '1'; wait for clk_period/2; end process; -- * Test Bench - User Defined Section * tb : PROCESS BEGIN rst <='1'; en<='0'; WAIT for 100ns; -- will wait forever rst<='0'; en<='1'; wait; END PROCESS; -- * End Test Bench - User Defined Section * END; 讯享网--ujs-lili library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_unsigned.ALL; use IEEE.STD_LOGIC_arith.ALL; entity jinzhi24 is port(clk,en,rst:in std_logic; cout:out std_logic; cq:out std_logic_vector(4 downto 0)); end jinzhi24; architecture Behavioral of jinzhi24 is signal cq1:std_logic_vector(4 downto 0):="00000"; begin process(clk,en,rst) begin if rst='1' then cout<='0';cq<="00000"; elsif clk'event and clk='1' then if en='1' then if cq1<"11000" then cq1<=cq1+'1'; else cq1<="00000"; cout<='1'; end if; end if; end if; if cq1<"11000" then cout<='0'; end if; cq<=cq1; end process; end Behavioral;

仿真:

2.硬件连接

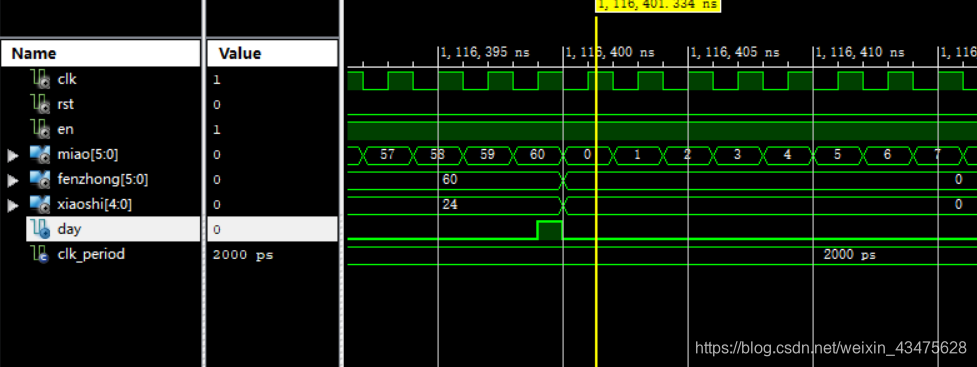

3.仿真:

仿真代码:

LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.numeric_std.ALL; LIBRARY UNISIM; USE UNISIM.Vcomponents.ALL; ENTITY yitian_top_yitian_top_sch_tb IS END yitian_top_yitian_top_sch_tb; ARCHITECTURE behavioral OF yitian_top_yitian_top_sch_tb IS COMPONENT yitian_top PORT( clk : IN STD_LOGIC; rst : IN STD_LOGIC; en : IN STD_LOGIC; miao : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); fenzhong : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); xiaoshi : OUT STD_LOGIC_VECTOR (4 DOWNTO 0); day : OUT STD_LOGIC); END COMPONENT; SIGNAL clk : STD_LOGIC; SIGNAL rst : STD_LOGIC; SIGNAL en : STD_LOGIC; SIGNAL miao : STD_LOGIC_VECTOR (5 DOWNTO 0); SIGNAL fenzhong : STD_LOGIC_VECTOR (5 DOWNTO 0); SIGNAL xiaoshi : STD_LOGIC_VECTOR (4 DOWNTO 0); SIGNAL day : STD_LOGIC; constant clk_period : time := 2 ns; BEGIN UUT: yitian_top PORT MAP( clk => clk, rst => rst, en => en, miao => miao, fenzhong => fenzhong, xiaoshi => xiaoshi, day => day ); clk_process :process begin clk <= '0'; wait for clk_period/2; clk <= '1'; wait for clk_period/2; end process; -- -- * Test Bench - User Defined Section * tb : PROCESS BEGIN rst <='1'; en<='0'; WAIT for 100ns; -- will wait forever rst<='0'; en<='1'; wait; END PROCESS; -- * -- * End Test Bench - User Defined Section * END;

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/40146.html