<svg xmlns="http://www.w3.org/2000/svg" style="display: none;"> <path stroke-linecap="round" d="M5,0 0,2.5 5,5z" id="raphael-marker-block" style="-webkit-tap-highlight-color: rgba(0, 0, 0, 0);"></path> </svg> 讯享网

1、运行电源电压高达 50V

2、PWM 运行频率高达 500kH

3、片内集成欠压、过温、过载和短路保护功能

4、片内集成欠压、过温、过载和短路保护功能

5、DRV83x2 需要两个电源,一个为 GVDD 和 VDD 提供

12V 电源,另一个为 PVDD 提供高达 50V 的电源

1、overview

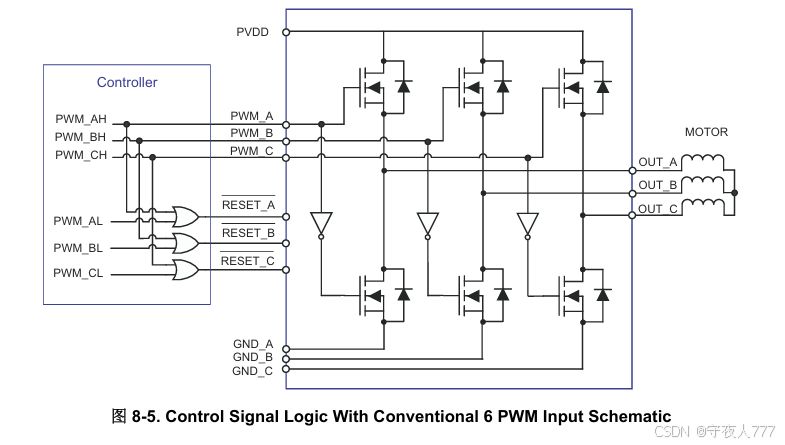

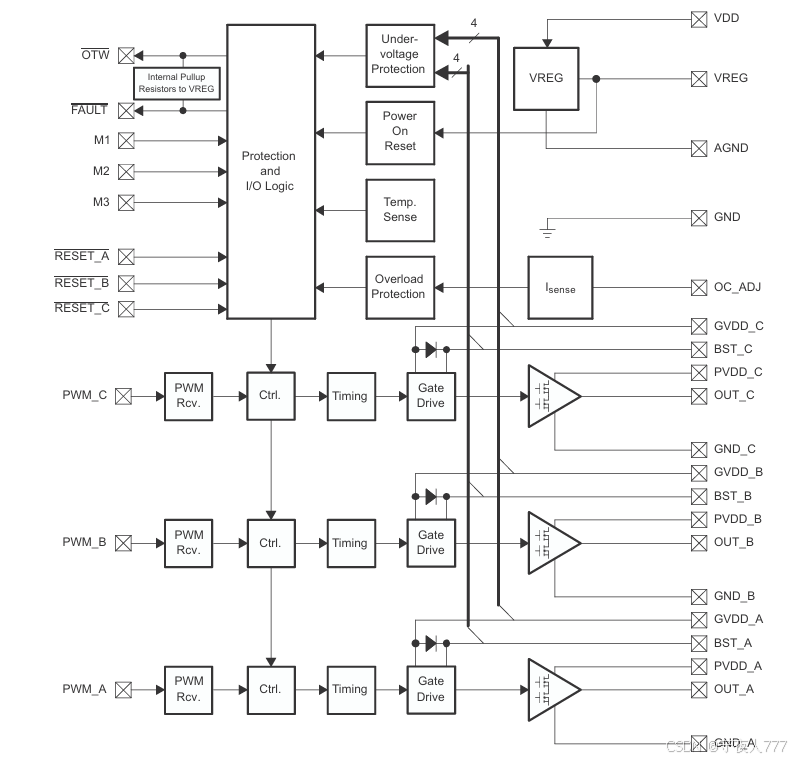

DRV83x2 器件有三个大电流半 H 桥输出,由六个输入 PWM_x 和 RESET_x 控制。 RESET_A 为低电平时,OUT_A 变为高阻抗,允许电流流过高压侧和低压侧 FET 的内部体二极管。 当 RESET_A 为高电平且 PWM_A 为低电平时,OUT_A 被驱动为低电平,其低端 FET 被启用。 当 RESET_A 为高电平且 PWM_A 为高电平时,OUT_A 将在其高压侧 FET 启用的情况下被驱动为高电平。 B 和 C 也是如此。

2、功能框图

3、功能描述

1、错误报告

故障和 OTW 引脚均为低电平有效、漏极开路输出。 它们的功能是向 PWM 控制器或其他系统控制设备发出保护模式信号。

任何导致设备关机的故障,如过热关机、过流关机或欠压保护,都会通过 FAULT 引脚变为低电平发出信号。 同样,结温超过 125°C。

任何导致设备关机的故障,如过热关机、过流关机或欠压保护,都会通过 FAULT 引脚变为低电平发出信号。 同样,结温超过 125°C

2、器件保护

DRV83x2 包含精心设计的高级保护电路,不仅便于系统集成和使用,还能保护器件不会因短路、过流、过热和欠压等各种故障条件而发生永久性故障。 DRV83x2 在发生故障时会立即将半桥输出设置为高阻抗 (Hi-Z) 状态,并将 FAULT 引脚置低。 在过流或过热以外的情况下,当故障条件消除或栅极电源电压升高时,器件会自动恢复。 为获得尽可能高的可靠性,在从过流关断 (OCSD) 或 OTSD 故障中恢复时,应在关断后 1 秒内从外部复位器件。

3、自举电容欠压保护

4、过流保护

DRV83x2 具有独立的快速反应电流检测器,所有高压侧和低压侧功率级 FET 均具有可编程跳闸阈值(OC阈值)。 通过模式选择引脚可对 OC 保护进行两种设置:逐周期 (CBC) 电流限制模式和 OC 锁存 (OCL) 关断模式。

在 CBC 限流模式下,探测器的输出由两个保护系统监控。 第一个保护系统控制功率级,以防止输出电流进一步增大,即执行 CBC 电流限制功能,而不是过早关闭设备。 这一功能可有效限制电机启动或瞬态期间的浪涌电流,而不会损坏设备。

短路至电源和短路至地期间,由于限流电路可能无法将电流控制在适当的水平,第二个保护系统会触发锁存关断,从而将相关半桥设置为高阻抗(Hi-Z)状态。 电流限制和过流保护分别独立于半桥 A、B 和 C。

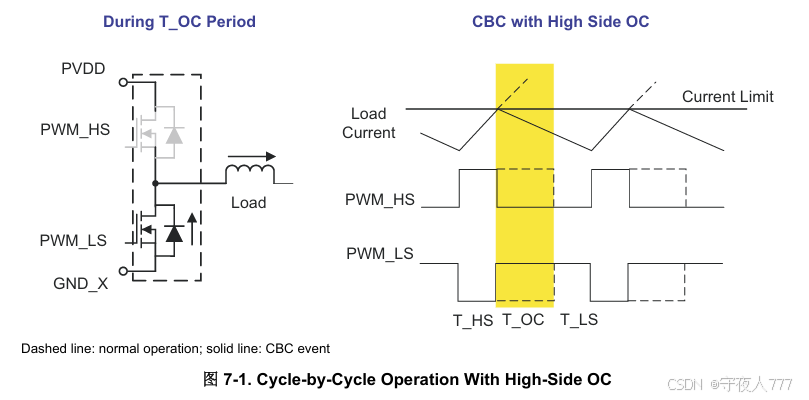

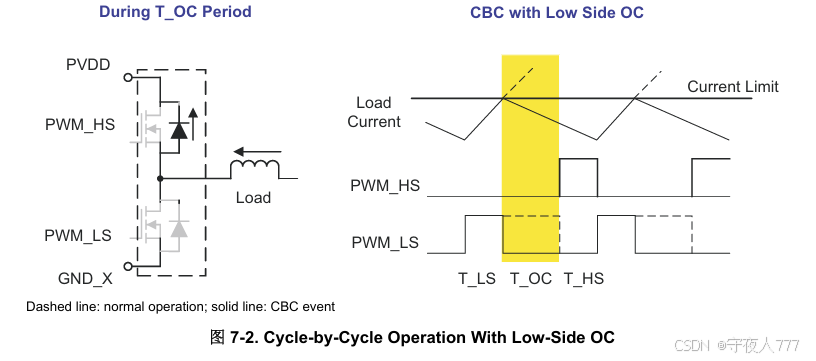

图 7-1 展示了高侧 OC 事件时的逐周期运行,图 7-2 展示了低侧 OC 时的逐周期运行。 虚线表示未触发 CBC 事件时的运行波形,实线表示触发 CBC 事件时的波形。 在 CBC 限流模式下,当检测到低压侧 FET OC 时,器件将关闭受影响的低压侧 FET,并保持同一半桥的高压侧 FET 关断,直至下一个 PWM 周期;当检测到高压侧 FET OC 时,器件将关闭受影响的高压侧 FET,并开启半桥的低压侧 FET,直至下一个 PWM 周期。

值得注意的是,如果在 CBC 中发生过流事件时,半桥的输入保持恒定值,那么在过流事件结束时,相关半桥将处于 HI-Z 状态。 循环 IN_X 将使 OUT_X 恢复正常工作。

在 OC 锁存关断模式下,CBC 电流限制和错误恢复电路被禁用,过流条件将导致设备关断。 关断后,必须断言 RESET_A、RESET_B 和,才能在过流条件消除后恢复正常工作。

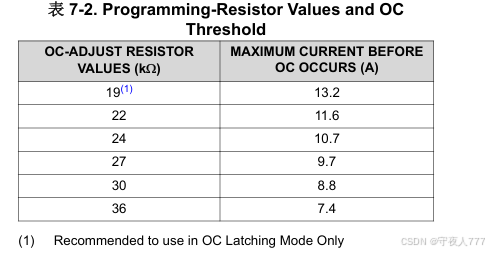

为了增加灵活性,OC阈值可通过连接在 OC_ADJ 引脚和 AGND 引脚之间的单个外部电阻进行编程。 有关编程电阻值与 OC 门限之间的相关信息,请参阅 7-2。

表 7-2 中的数值显示了给定电阻器的典型 OC 门限。 假设多个器件的 OC_ADJ 引脚电阻固定不变,则 OC 门限测量值的器件间差异可能为 20%。 因此,该功能设计用于系统保护,而非精确的电流控制。

需要注意的是,过流检测器正常工作的前提是在功率级输出端存在适当的电感器或功率铁氧体磁珠。 如果功率级输出引脚直接短路,则无法确保短路保护。

5、过温保护

DRV83x2 具有两级温度保护系统,当器件结温超过 125°C(标称值)时,系统会发出低电平有效警告信号(OTW);当器件结温超过 150°C(标称值)时,器件会进入热关断状态,从而将所有半桥输出设置为高阻抗(Hi-Z)状态,并将 FAULT 设为低电平。 在这种情况下,OTSD 被锁存,必须将 RESET_B 和 RESET_C 置低才能清除锁存。

6、欠压保护 (UVP) 和上电复位 (POR)

DRV83x2 的 UVP 和 POR 电路可在任何上电/掉电和掉电情况下全面保护器件。 上电时,当 GVDD_X 和 VDD 电源电压达到 9.8 V(典型值)时,POR 电路会复位过流电路,并确保所有电路完全正常工作。 虽然 GVDD_X 和 VDD 是独立监控的,但如果任何 VDD 或 GVDD_X 引脚上的电源电压降至 UVP 门限以下,所有半桥输出将立即设置为高阻抗 (Hi-Z) 状态,并将 FAULT 设为低电平。 当自举电容器上的所有电源电压都上升到 UVP 门限以上时,器件会自动恢复运行。

7、器件重启

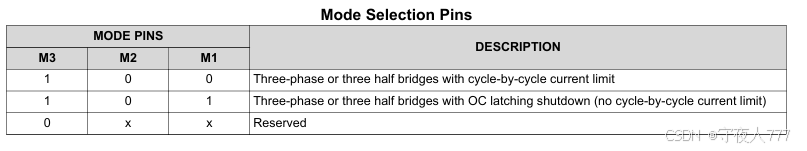

DRV83x2 支持两种不同的运行模式:

1、带 CBC 电流限值的三相 (3PH) 或三个半桥 (HB)

2、带 OC 锁定关断(无 CBC 电流限制),三相或三个半桥

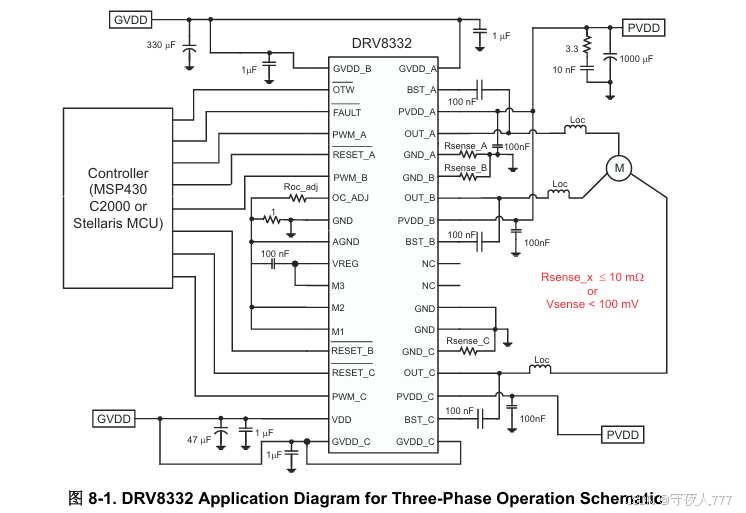

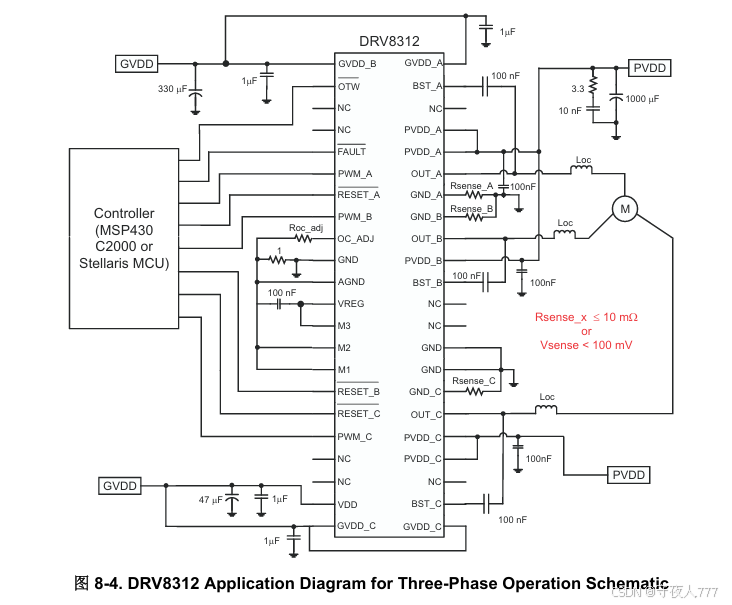

由于每个半桥都有独立的电源和接地引脚,因此可在 PVDD 至 PVDD_X 或 GND_X 至 GND(地平面)之间插入一个分流检测电阻。 建议在 PVDD 和 PVDD_X 之间的高压侧分流电阻用于差分电流检测,因为低压侧检测的高偏置电压可能会影响器件的工作。 如果必须使用低压侧传感,建议分流电阻值为 10 mΩ 或更小,或传感电压为 100 mV 或更小。

图 8-1 和图 8-4 显示了三相应用示例,图 8-5 显示了如何通过一些简单的逻辑连接 DRV83x2,以适应传统的 6 PWM 输入控制。

TI建议在相位切换时使用互补控制方案,以防止环流能量在相位内流动,并使电流限制功能始终处于激活状态。 互补控制方案还能迫使电流始终流经感应电阻器,从而实现更好的电流感应和系统控制。

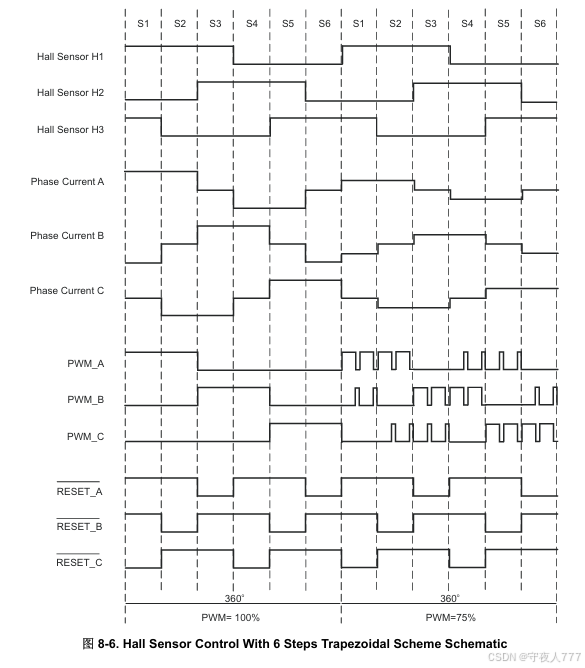

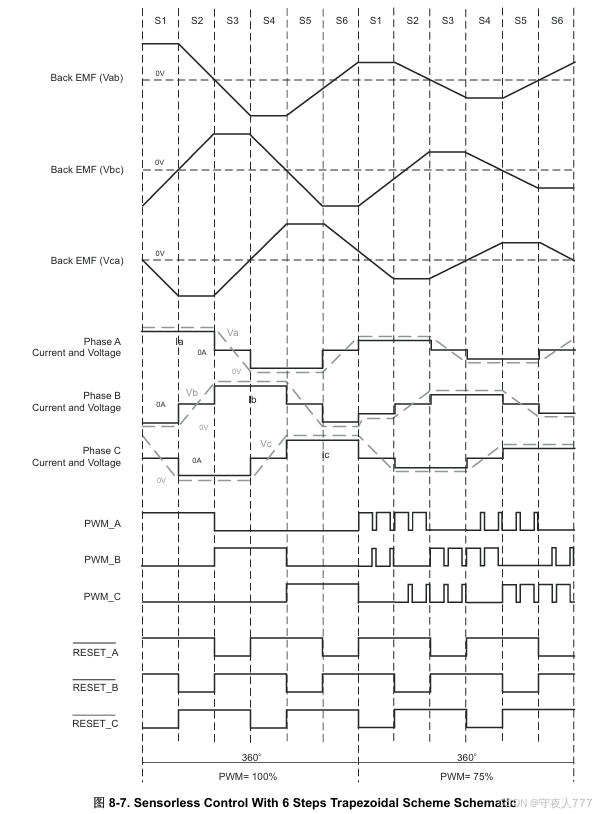

图 8-6 显示了采用霍尔传感器控制的六步换向方案,图 8-7 显示了采用无传感器控制的六步换向方案。 实际应用中的霍尔传感器顺序可能与图 8-6 所示不同,这取决于所使用的电机。 请查阅电机制造商的数据手册,了解应用中的正确顺序。 在六步换向互补控制方案中,占空比大于 50% 的半桥电流为正,占空比小于 50% 的半桥电流为负。 正常运行时,将 PWM 占空比从 50% 变为 100%,电流将从 0 调整为六步控制的最大值。 建议在低压侧的每个开关周期应用至少 50 ns 至 100 ns 的 PWM 脉冲,以便对自举电容正确充电。 低压侧 FET 的最小脉冲影响很小,例如,低压侧最小脉冲为 100 ns 时,最大占空比为 99.9%。 RESET_X 引脚可用于使通道 X 进入高阻抗模式。 如果您希望 PWM 开关一个通道,但另一个通道的低端场效应管保持导通(第三个通道处于高阻抗模式),以实现双象限模式,则可使用 OT 锁定关断模式。

DRV83x2 还可用于正弦波形控制和面向场的控制。 有关控制算法,请查看 TI 网站 MCU 电机控制库。

1、VREG

VREG 引脚用于内部逻辑,不得用作外部电路的电压源。 VREG 引脚上的电容应连接至 AGND。

2、VDD

VDD 引脚中的瞬态电流可能大大高于通过 VDD 引脚的平均电流。 因此,应使用通向 GVDD 的低电阻路径。 应在 VDD 引脚上放置一个 22µF 至 47µF 的电容器,与 100nF 至 1µF 的去耦电容器并排,以便在瞬态期间提供恒定电压。

3、OTW

OTW 报告表明器件接近高结温。 该信号可与 MCU 配合使用,在 OTW 低电平时降低系统功率,以防止 OT 在较高温度下关断。 3.3V 逻辑无需外部上拉电阻或 3.3V 电源。 OTW 引脚有一个连接到内部 3.3V 的内部上拉电阻,以减少外部元件数量。 对于 5V 逻辑,则需要一个连接至 5V 的外部上拉电阻。

4、FAULT

故障引脚可报告导致设备关机的任何故障情况。 3.3V 逻辑无需外部上拉电阻或 3.3V 电源。 故障引脚有一个连接到内部 3.3V 的内部上拉电阻,以减少外部元件数量。 对于 5V 逻辑,需要一个外部上拉电阻连接至 5V。

5、OC_ADJ

为了精确控制过流保护,OC_ADJ 引脚必须通过一个 OC 调节电阻器连接到 AGND。

6、 PWM_X 和 RESET_X

建议在不使用这些引脚时将其连接到 AGND 或 GND,这些引脚仅支持 3.3V 逻辑。

7、M123

模式选择引脚(M1、M2 和 M3)应连接至 VREG(逻辑高电平)或 AGND(逻辑低电平)。 如果 AGND 和 GND 之间使用 1Ω 电阻,则不建议将模式引脚连接到电路板接地。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/181051.html