任务1:

在 中实现如下函数:

1.cache结构体:

1.根据读的要求设置了tag , valid_bit , dirty_bit; 根据回的要求设置了dirty_bit。

2.根据主存地址划分:

- cache有16KB(2^14) , 主存大小有32KB(2^15) ,块大小有2^6 bit , 且是按四路组相联来处理的;

- 那么块内偏移为6位 ,cache行号有2^8行(因为14 - 6 = 8,cache容量处以每个块的大小)。

- 因为是四路组相联,所以cache组数等于cache行号处以每组的行数(4),即2(8-2)=26;

- 那么现在主存地址有15位:tag = 15 -块内偏移长度(6) - cache组号(6)= 3。

讯享网

2.init_cache()函数:

- 很简单,就是算出cache的总行数;

- 遍历所有的cache行,将每个cache行的有效位和脏位置0;

讯享网

3.uint32_t cache_read(uintptr_t addr)函数:

1.总思路:

分为三个部分:主存地址进来

若命中:

(1)按主存地址先访问cache,如果命中,返回数据;

若不命中:

(2)在cache中找空闲行,即判断valid_bit是否为0,如果为0,则将此cache行作为新的读入的数据存放的地方;

(3)如果该cache组是全部满的,即所有的valid_bit为1,那么随便取一行,此时先判断脏位是否为1,为1的话就将当前的cache行先写回主存,再则将此cache行作为新的读入的数据存放的地方;

2.分情况说明:

4. cache_write(uintptr_t addr, uint32_t data, uint32_t wmask) 函数:

1.总思路:

分为三个部分:主存地址进来,和读的函数是一样的。

若命中:

(1)按主存地址先访问cache,如果命中,则将掩码对应的偏移处的值修改;

若不命中:

(2)在cache中找空闲行,即判断valid_bit是否为0,如果为0,则将此cache行作为新的读入数据的地方,并将掩码对应的偏移处的值修改;

(3)如果该cache组是全部满的,即所有的valid_bit为1,那么随便取一行,此时先判断脏位是否为1,为1的话就将当前的cache行先写回主存,再则将此cache行作为新的读入的数据存放的地方 , 并将掩码对应的偏移处的值修改;

2.分情况说明:

这里调用到了一个cache_alter()函数,作用是设置掩码对应的偏移处的值修改:

- 在这里说明一下,因为那个mem_read()和mem_write()函数的第二个参数,即数据区的参数都是uint8_t的,所有设置数据区的时候都是按一个一个字节来存,但这样就造成了很不方便的地方,每次将数据返回时要把四个字节拼在一起,每次写完了之后还要将每个字节分散开写回到cache的数据区,真的很不方便。

- 在对比uncache_read的时候那个*p来了这么一个秒操作,( Data & (~wmask) ) | (data &wmask)这个也是仿照着它写的,就是掩码的地方修改,其它非掩码的字节不变。原来还傻傻地把掩码分情况讨论了。

- 最后改完之后,再分散到cache数据区的每个字节。

讯享网

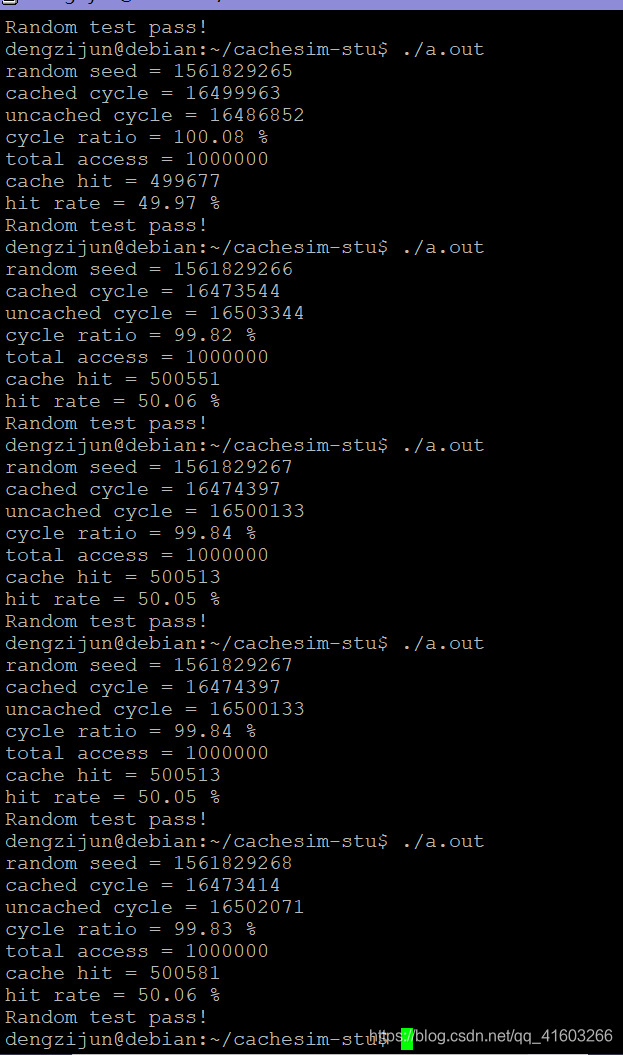

截图:

1.数据对齐和存储层次结构:

因为对齐的话更有利于访存的进行;比如int类型的数是按四字节对齐的,如果没有对齐,它是紧凑排列的话每次访存都要从头开始一个一个依次查询,时间消耗变大。就好像链表和数组,链表是没有对齐的,每次访存都要从链表头开始;而数组只要知道它的首地址和访存第几个,就可以计算出访存地址。

这可太多了:

1.写回的时候误用了新的cache行的主存块号:

这是有点隐晦的错误了,就是在写了之后就会给报错,在随机替换的时候错了,那这就是写回的时候有问题,写错地方了,改了之后就是把旧的主存块号拼出来,用它。

2.随即替换时写的顺序错了:

原来被绕进去了,是应该先写回主存块呢,还是先写进cache行,再写回主存块呢?为什么会这样,那原来那块如果改过怎么办?于是明白了应该先写回再装入新的。

3.数据区的大小设置:

这就太坑了,因为mem_read和write函数入口参数类型的误导,致使我们做了很多单字节转四字节和四字节转单字节的操作,好烦心好累,明明可以强制类型转化,最后才发现。

这就是写回的时候有问题,写错地方了,改了之后就是把旧的主存块号拼出来,用它。

2.随即替换时写的顺序错了:

原来被绕进去了,是应该先写回主存块呢,还是先写进cache行,再写回主存块呢?为什么会这样,那原来那块如果改过怎么办?于是明白了应该先写回再装入新的。

3.数据区的大小设置:

这就太坑了,因为mem_read和write函数入口参数类型的误导,致使我们做了很多单字节转四字节和四字节转单字节的操作,好烦心好累,明明可以强制类型转化,最后才发现。

爽。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/176960.html