【实例简介】ARM64 完整指令集,学习必备<br /> 讯享网

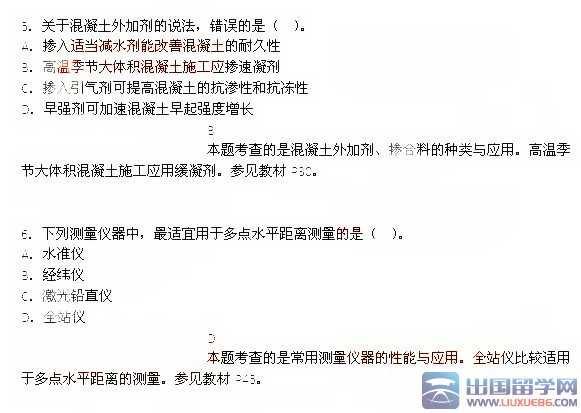

讯享网【实例截图】 <img src="https://img01.haolizi.net/2022/07/25/e8/5/5/ec35adb1.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/7c/d/5/7cd531a126dbe747fac19dbb.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/18/0/7/2add29ef4985cd6703f3e.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/bf/6/7/bf670bdeb553f720b15b42374.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/40/4/a/404ab39de8f6b79d7bd033bd8041a29c.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/92/d/c/92dcbd0942dea5ba32233c08767e58f6.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/c2/a/e/c2aeb72d2effc942c6f876de03.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/1c/8/0/1c80b16fd99fbf419d63e61f5.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/e8/3/8/eb82ff563bdda.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/73/7/8/7378f446a4bf0c7.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/25/8/0/25807efa0e19e8a958a8c0d.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/2d/2/0/2d200a8f0e9b40f611d3db00baae24e3.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/63/b/4/63b4066a4fe6945b043633f9f0e771e0.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/68/0/1/aad3c7b9955ae458dc.png" alt="" /><img src="https://img01.haolizi.net/2022/07/25/2e/7/1/2e71c730ace5a78fcd8d2afcf4.png" alt="" />

讯享网【核心代码】 <div> A64 -- Base Instructions (alphabetic order) </div> <div> ADC: Add with Carry. </div> <div> ADCS: Add with Carry, setting flags. </div> <div> ADD (extended register): Add (extended register). </div> <div> ADD (immediate): Add (immediate). </div> <div> ADD (shifted register): Add (shifted register). </div> <div> ADDG: Add with Tag. </div> <div> ADDS (extended register): Add (extended register), setting flags. </div> <div> ADDS (immediate): Add (immediate), setting flags. </div> <div> ADDS (shifted register): Add (shifted register), setting flags. </div> <div> ADR: Form PC-relative address. </div> <div> ADRP: Form PC-relative address to 4KB page. </div> <div> AND (immediate): Bitwise AND (immediate). </div> <div> AND (shifted register): Bitwise AND (shifted register). </div> <div> ANDS (immediate): Bitwise AND (immediate), setting flags. </div> <div> ANDS (shifted register): Bitwise AND (shifted register), setting flags. </div> <div> ASR (immediate): Arithmetic Shift Right (immediate): an alias of SBFM. </div> <div> ASR (register): Arithmetic Shift Right (register): an alias of ASRV. </div> <div> ASRV: Arithmetic Shift Right Variable. </div> <div> AT: Address Translate: an alias of SYS. </div> <div> AUTDA, AUTDZA: Authenticate Data address, using key A. </div> <div> AUTDB, AUTDZB: Authenticate Data address, using key B. </div> <div> AUTIA, AUTIA1716, AUTIASP, AUTIAZ, AUTIZA: Authenticate Instruction address, using key A. </div> <div> AUTIB, AUTIB1716, AUTIBSP, AUTIBZ, AUTIZB: Authenticate Instruction address, using key B. </div> <div> AXFLAG: Convert floating-point condition flags from Arm to external format. </div> <div> B: Branch. </div> <div> B.cond: Branch conditionally. </div> <div> BC.cond: Branch Consistent conditionally. </div> <div> BFC: Bitfield Clear: an alias of BFM. </div> <div> BFI: Bitfield Insert: an alias of BFM. </div> <div> BFM: Bitfield Move. </div> <div> BFXIL: Bitfield extract and insert at low end: an alias of BFM. </div> <div> BIC (shifted register): Bitwise Bit Clear (shifted register). </div> <div> BICS (shifted register): Bitwise Bit Clear (shifted register), setting flags. </div> <div> BL: Branch with Link. </div> <div> Page 2A64 -- Base Instructions (alphabetic order) </div> <div> BLR: Branch with Link to Register. </div> <div> BLRAA, BLRAAZ, BLRAB, BLRABZ: Branch with Link to Register, with pointer authentication. </div> <div> BR: Branch to Register. </div> <div> BRAA, BRAAZ, BRAB, BRABZ: Branch to Register, with pointer authentication. </div> <div> BRB: Branch Record Buffer: an alias of SYS. </div> <div> BRK: Breakpoint instruction. </div> <div> BTI: Branch Target Identification. </div> <div> CAS, CASA, CASAL, CASL: Compare and Swap word or doubleword in memory. </div> <div> CASB, CASAB, CASALB, CASLB: Compare and Swap byte in memory. </div> <div> CASH, CASAH, CASALH, CASLH: Compare and Swap halfword in memory. </div> <div> CASP, CASPA, CASPAL, CASPL: Compare and Swap Pair of words or doublewords in memory. </div> <div> CBNZ: Compare and Branch on Nonzero. </div> <div> CBZ: Compare and Branch on Zero. </div> <div> CCMN (immediate): Conditional Compare Negative (immediate). </div> <div> CCMN (register): Conditional Compare Negative (register). </div> <div> CCMP (immediate): Conditional Compare (immediate). </div> <div> CCMP (register): Conditional Compare (register). </div> <div> CFINV: Invert Carry Flag. </div> <div> CFP: Control Flow Prediction Restriction by Context: an alias of SYS. </div> <div> CINC: Conditional Increment: an alias of CSINC. </div> <div> CINV: Conditional Invert: an alias of CSINV. </div> <div> CLREX: Clear Exclusive. </div> <div> CLS: Count Leading Sign bits. </div> <div> CLZ: Count Leading Zeros. </div> <div> CMN (extended register): Compare Negative (extended register): an alias of ADDS (extended register). </div> <div> CMN (immediate): Compare Negative (immediate): an alias of ADDS (immediate). </div> <div> CMN (shifted register): Compare Negative (shifted register): an alias of ADDS (shifted register). </div> <div> CMP (extended register): Compare (extended register): an alias of SUBS (extended register). </div> <div> CMP (immediate): Compare (immediate): an alias of SUBS (immediate). </div> <div> CMP (shifted register): Compare (shifted register): an alias of SUBS (shifted register). </div> <div> CMPP: Compare with Tag: an alias of SUBPS. </div> <div> CNEG: Conditional Negate: an alias of CSNEG. </div> <div> CPP: Cache Prefetch Prediction Restriction by Context: an alias of SYS. </div> <div> CPYFP, CPYFM, CPYFE: Memory Copy Forward-only. </div> <div> CPYFPN, CPYFMN, CPYFEN: Memory Copy Forward-only, reads and writes non-temporal. </div> <div> CPYFPRN, CPYFMRN, CPYFERN: Memory Copy Forward-only, reads non-temporal. </div> <div> Page 3A64 -- Base Instructions (alphabetic order) </div> <div> CPYFPRT, CPYFMRT, CPYFERT: Memory Copy Forward-only, reads unprivileged. </div> <div> CPYFPRTN, CPYFMRTN, CPYFERTN: Memory Copy Forward-only, reads unprivileged, reads and writes non-temporal. </div> <div> CPYFPRTRN, CPYFMRTRN, CPYFERTRN: Memory Copy Forward-only, reads unprivileged and non-temporal. </div> <div> CPYFPRTWN, CPYFMRTWN, CPYFERTWN: Memory Copy Forward-only, reads unprivileged, writes non-temporal. </div> <div> CPYFPT, CPYFMT, CPYFET: Memory Copy Forward-only, reads and writes unprivileged. </div> <div> CPYFPTN, CPYFMTN, CPYFETN: Memory Copy Forward-only, reads and writes unprivileged and non-temporal. </div> <div> CPYFPTRN, CPYFMTRN, CPYFETRN: Memory Copy Forward-only, reads and writes unprivileged, reads non-temporal. </div> <div> CPYFPTWN, CPYFMTWN, CPYFETWN: Memory Copy Forward-only, reads and writes unprivileged, writes non </div> <div> temporal. </div> <div> CPYFPWN, CPYFMWN, CPYFEWN: Memory Copy Forward-only, writes non-temporal. </div> <div> CPYFPWT, CPYFMWT, CPYFEWT: Memory Copy Forward-only, writes unprivileged. </div> <div> CPYFPWTN, CPYFMWTN, CPYFEWTN: Memory Copy Forward-only, writes unprivileged, reads and writes non </div> <div> temporal. </div> <div> CPYFPWTRN, CPYFMWTRN, CPYFEWTRN: Memory Copy Forward-only, writes unprivileged, reads non-temporal. </div> <div> CPYFPWTWN, CPYFMWTWN, CPYFEWTWN: Memory Copy Forward-only, writes unprivileged and non-temporal. </div> <div> CPYP, CPYM, CPYE: Memory Copy. </div> <div> CPYPN, CPYMN, CPYEN: Memory Copy, reads and writes non-temporal. </div> <div> CPYPRN, CPYMRN, CPYERN: Memory Copy, reads non-temporal. </div> <div> CPYPRT, CPYMRT, CPYERT: Memory Copy, reads unprivileged. </div> <div> CPYPRTN, CPYMRTN, CPYERTN: Memory Copy, reads unprivileged, reads and writes non-temporal. </div> <div> CPYPRTRN, CPYMRTRN, CPYERTRN: Memory Copy, reads unprivileged and non-temporal. </div> <div> CPYPRTWN, CPYMRTWN, CPYERTWN: Memory Copy, reads unprivileged, writes non-temporal. </div> <div> CPYPT, CPYMT, CPYET: Memory Copy, reads and writes unprivileged. </div> <div> CPYPTN, CPYMTN, CPYETN: Memory Copy, reads and writes unprivileged and non-temporal. </div> <div> CPYPTRN, CPYMTRN, CPYETRN: Memory Copy, reads and writes unprivileged, reads non-temporal. </div> <div> CPYPTWN, CPYMTWN, CPYETWN: Memory Copy, reads and writes unprivileged, writes non-temporal. </div> <div> CPYPWN, CPYMWN, CPYEWN: Memory Copy, writes non-temporal. </div> <div> CPYPWT, CPYMWT, CPYEWT: Memory Copy, writes unprivileged. </div> <div> CPYPWTN, CPYMWTN, CPYEWTN: Memory Copy, writes unprivileged, reads and writes non-temporal. </div> <div> CPYPWTRN, CPYMWTRN, CPYEWTRN: Memory Copy, writes unprivileged, reads non-temporal. </div> <div> CPYPWTWN, CPYMWTWN, CPYEWTWN: Memory Copy, writes unprivileged and non-temporal. </div> <div> CRC32B, CRC32H, CRC32W, CRC32X: CRC32 checksum. </div> <div> CRC32CB, CRC32CH, CRC32CW, CRC32CX: CRC32C checksum. </div> <div> CSDB: Consumption of Speculative Data Barrier. </div> <div> CSEL: Conditional Select. </div> <div> CSET: Conditional Set: an alias of CSINC. </div> <div> CSETM: Conditional Set Mask: an alias of CSINV. </div> <div> Page 4A64 -- Base Instructions (alphabetic order) </div> <div> CSINC: Conditional Select Increment. </div> <div> CSINV: Conditional Select Invert. </div> <div> CSNEG: Conditional Select Negation. </div> <div> DC: Data Cache operation: an alias of SYS. </div> <div> DCPS1: Debug Change PE State to EL1.. </div> <div> DCPS2: Debug Change PE State to EL2.. </div> <div> DCPS3: Debug Change PE State to EL3. </div> <div> DGH: Data Gathering Hint. </div> <div> DMB: Data Memory Barrier. </div> <div> DRPS: Debug restore process state. </div> <div> DSB: Data Synchronization Barrier. </div> <div> DVP: Data Value Prediction Restriction by Context: an alias of SYS. </div> <div> EON (shifted register): Bitwise Exclusive OR NOT (shifted register). </div> <div> EOR (immediate): Bitwise Exclusive OR (immediate). </div> <div> EOR (shifted register): Bitwise Exclusive OR (shifted register). </div> <div> ERET: Exception Return. </div> <div> ERETAA, ERETAB: Exception Return, with pointer authentication. </div> <div> ESB: Error Synchronization Barrier. </div> <div> EXTR: Extract register. </div> <div> GMI: Tag Mask Insert. </div> <div> HINT: Hint instruction. </div> <div> HLT: Halt instruction. </div> <div> HVC: Hypervisor Call. </div> <div> IC: Instruction Cache operation: an alias of SYS. </div> <div> IRG: Insert Random Tag. </div> <div> ISB: Instruction Synchronization Barrier. </div> <div> LD64B: Single-copy Atomic 64-byte Load. </div> <div> LDADD, LDADDA, LDADDAL, LDADDL: Atomic add on word or doubleword in memory. </div> <div> LDADDB, LDADDAB, LDADDALB, LDADDLB: Atomic add on byte in memory. </div> <div> LDADDH, LDADDAH, LDADDALH, LDADDLH: Atomic add on halfword in memory. </div> <div> LDAPR: Load-Acquire RCpc Register. </div> <div> LDAPRB: Load-Acquire RCpc Register Byte. </div> <div> LDAPRH: Load-Acquire RCpc Register Halfword. </div> <div> LDAPUR: Load-Acquire RCpc Register (unscaled). </div> <div> LDAPURB: Load-Acquire RCpc Register Byte (unscaled). </div> <div> LDAPURH: Load-Acquire RCpc Register Halfword (unscaled). </div> <div> Page 5A64 -- Base Instructions (alphabetic order) </div> <div> LDAPURSB: Load-Acquire RCpc Register Signed Byte (unscaled). </div> <div> LDAPURSH: Load-Acquire RCpc Register Signed Halfword (unscaled). </div> <div> LDAPURSW: Load-Acquire RCpc Register Signed Word (unscaled). </div> <div> LDAR: Load-Acquire Register. </div> <div> LDARB: Load-Acquire Register Byte. </div> <div> LDARH: Load-Acquire Register Halfword. </div> <div> LDAXP: Load-Acquire Exclusive Pair of Registers. </div> <div> LDAXR: Load-Acquire Exclusive Register. </div> <div> LDAXRB: Load-Acquire Exclusive Register Byte. </div> <div> LDAXRH: Load-Acquire Exclusive Register Halfword. </div> <div> LDCLR, LDCLRA, LDCLRAL, LDCLRL: Atomic bit clear on word or doubleword in memory. </div> <div> LDCLRB, LDCLRAB, LDCLRALB, LDCLRLB: Atomic bit clear on byte in memory. </div> <div> LDCLRH, LDCLRAH, LDCLRALH, LDCLRLH: Atomic bit clear on halfword in memory. </div> <div> LDEOR, LDEORA, LDEORAL, LDEORL: Atomic exclusive OR on word or doubleword in memory. </div> <div> LDEORB, LDEORAB, LDEORALB, LDEORLB: Atomic exclusive OR on byte in memory. </div> <div> LDEORH, LDEORAH, LDEORALH, LDEORLH: Atomic exclusive OR on halfword in memory. </div> <div> LDG: Load Allocation Tag. </div> <div> LDGM: Load Tag Multiple. </div> <div> LDLAR: Load LOAcquire Register. </div> <div> LDLARB: Load LOAcquire Register Byte. </div> <div> LDLARH: Load LOAcquire Register Halfword. </div> <div> LDNP: Load Pair of Registers, with non-temporal hint. </div> <div> LDP: Load Pair of Registers. </div> <div> LDPSW: Load Pair of Registers Signed Word. </div> <div> LDR (immediate): Load Register (immediate). </div> <div> LDR (literal): Load Register (literal). </div> <div> LDR (register): Load Register (register). </div> <div> LDRAA, LDRAB: Load Register, with pointer authentication. </div> <div> LDRB (immediate): Load Register Byte (immediate). </div> <div> LDRB (register): Load Register Byte (register). </div> <div> LDRH (immediate): Load Register Halfword (immediate). </div> <div> LDRH (register): Load Register Halfword (register). </div> <div> LDRSB (immediate): Load Register Signed Byte (immediate). </div> <div> LDRSB (register): Load Register Signed Byte (register). </div> <div> LDRSH (immediate): Load Register Signed Halfword (immediate). </div> <div> LDRSH (register): Load Register Signed Halfword (register). </div> <div> Page 6A64 -- Base Instructions (alphabetic order) </div> <div> LDRSW (immediate): Load Register Signed Word (immediate). </div> <div> LDRSW (literal): Load Register Signed Word (literal). </div> <div> LDRSW (register): Load Register Signed Word (register). </div> <div> LDSET, LDSETA, LDSETAL, LDSETL: Atomic bit set on word or doubleword in memory. </div> <div> LDSETB, LDSETAB, LDSETALB, LDSETLB: Atomic bit set on byte in memory. </div> <div> LDSETH, LDSETAH, LDSETALH, LDSETLH: Atomic bit set on halfword in memory. </div> <div> LDSMAX, LDSMAXA, LDSMAXAL, LDSMAXL: Atomic signed maximum on word or doubleword in memory. </div> <div> LDSMAXB, LDSMAXAB, LDSMAXALB, LDSMAXLB: Atomic signed maximum on byte in memory. </div> <div> LDSMAXH, LDSMAXAH, LDSMAXALH, LDSMAXLH: Atomic signed maximum on halfword in memory. </div> <div> LDSMIN, LDSMINA, LDSMINAL, LDSMINL: Atomic signed minimum on word or doubleword in memory. </div> <div> LDSMINB, LDSMINAB, LDSMINALB, LDSMINLB: Atomic signed minimum on byte in memory. </div> <div> LDSMINH, LDSMINAH, LDSMINALH, LDSMINLH: Atomic signed minimum on halfword in memory. </div> <div> LDTR: Load Register (unprivileged). </div> <div> LDTRB: Load Register Byte (unprivileged). </div> <div> LDTRH: Load Register Halfword (unprivileged). </div> <div> LDTRSB: Load Register Signed Byte (unprivileged). </div> <div> LDTRSH: Load Register Signed Halfword (unprivileged). </div> <div> LDTRSW: Load Register Signed Word (unprivileged). </div> <div> LDUMAX, LDUMAXA, LDUMAXAL, LDUMAXL: Atomic unsigned maximum on word or doubleword in memory. </div> <div> LDUMAXB, LDUMAXAB, LDUMAXALB, LDUMAXLB: Atomic unsigned maximum on byte in memory. </div> <div> LDUMAXH, LDUMAXAH, LDUMAXALH, LDUMAXLH: Atomic unsigned maximum on halfword in memory. </div> <div> LDUMIN, LDUMINA, LDUMINAL, LDUMINL: Atomic unsigned minimum on word or doubleword in memory. </div> <div> LDUMINB, LDUMINAB, LDUMINALB, LDUMINLB: Atomic unsigned minimum on byte in memory. </div> <div> LDUMINH, LDUMINAH, LDUMINALH, LDUMINLH: Atomic unsigned minimum on halfword in memory. </div> <div> LDUR: Load Register (unscaled). </div> <div> LDURB: Load Register Byte (unscaled). </div> <div> LDURH: Load Register Halfword (unscaled). </div> <div> LDURSB: Load Register Signed Byte (unscaled). </div> <div> LDURSH: Load Register Signed Halfword (unscaled). </div> <div> LDURSW: Load Register Signed Word (unscaled). </div> <div> LDXP: Load Exclusive Pair of Registers. </div> <div> LDXR: Load Exclusive Register. </div> <div> LDXRB: Load Exclusive Register Byte. </div> <div> LDXRH: Load Exclusive Register Halfword. </div> <div> LSL (immediate): Logical Shift Left (immediate): an alias of UBFM. </div> <div> LSL (register): Logical Shift Left (register): an alias of LSLV. </div> <div> Page 7A64 -- Base Instructions (alphabetic order) </div> <div> LSLV: Logical Shift Left Variable. </div> <div> LSR (immediate): Logical Shift Right (immediate): an alias of UBFM. </div> <div> LSR (register): Logical Shift Right (register): an alias of LSRV. </div> <div> LSRV: Logical Shift Right Variable. </div> <div> MADD: Multiply-Add. </div> <div> MNEG: Multiply-Negate: an alias of MSUB. </div> <div> MOV (bitmask immediate): Move (bitmask immediate): an alias of ORR (immediate). </div> <div> MOV (inverted wide immediate): Move (inverted wide immediate): an alias of MOVN. </div> <div> MOV (register): Move (register): an alias of ORR (shifted register). </div> <div> MOV (to/from SP): Move between register and stack pointer: an alias of ADD (immediate). </div> <div> MOV (wide immediate): Move (wide immediate): an alias of MOVZ. </div> <div> MOVK: Move wide with keep. </div> <div> MOVN: Move wide with NOT. </div> <div> MOVZ: Move wide with zero. </div> <div> MRS: Move System Register. </div> <div> MSR (immediate): Move immediate value to Special Register. </div> <div> MSR (register): Move general-purpose register to System Register. </div> <div> MSUB: Multiply-Subtract. </div> <div> MUL: Multiply: an alias of MADD. </div> <div> MVN: Bitwise NOT: an alias of ORN (shifted register). </div> <div> NEG (shifted register): Negate (shifted register): an alias of SUB (shifted register). </div> <div> NEGS: Negate, setting flags: an alias of SUBS (shifted register). </div> <div> NGC: Negate with Carry: an alias of SBC. </div> <div> NGCS: Negate with Carry, setting flags: an alias of SBCS. </div> <div> NOP: No Operation. </div> <div> ORN (shifted register): Bitwise OR NOT (shifted register). </div> <div> ORR (immediate): Bitwise OR (immediate). </div> <div> ORR (shifted register): Bitwise OR (shifted register). </div> <div> PACDA, PACDZA: Pointer Authentication Code for Data address, using key A. </div> <div> PACDB, PACDZB: Pointer Authentication Code for Data address, using key B. </div> <div> PACGA: Pointer Authentication Code, using Generic key. </div> <div> PACIA, PACIA1716, PACIASP, PACIAZ, PACIZA: Pointer Authentication Code for Instruction address, using key A. </div> <div> PACIB, PACIB1716, PACIBSP, PACIBZ, PACIZB: Pointer Authentication Code for Instruction address, using key B. </div> <div> PRFM (immediate): Prefetch Memory (immediate). </div> <div> PRFM (literal): Prefetch Memory (literal). </div> <div> PRFM (register): Prefetch Memory (register). </div> <div> Page 8A64 -- Base Instructions (alphabetic order) </div> <div> PRFUM: Prefetch Memory (unscaled offset). </div> <div> PSB CSYNC: Profiling Synchronization Barrier. </div> <div> PSSBB: Physical Speculative Store Bypass Barrier: an alias of DSB. </div> <div> RBIT: Reverse Bits. </div> <div> RET: Return from subroutine. </div> <div> RETAA, RETAB: Return from subroutine, with pointer authentication. </div> <div> REV: Reverse Bytes. </div> <div> REV16: Reverse bytes in 16-bit halfwords. </div> <div> REV32: Reverse bytes in 32-bit words. </div> <div> REV64: Reverse Bytes: an alias of REV. </div> <div> RMIF: Rotate, Mask Insert Flags. </div> <div> ROR (immediate): Rotate right (immediate): an alias of EXTR. </div> <div> ROR (register): Rotate Right (register): an alias of RORV. </div> <div> RORV: Rotate Right Variable. </div> <div> SB: Speculation Barrier. </div> <div> SBC: Subtract with Carry. </div> <div> SBCS: Subtract with Carry, setting flags. </div> <div> SBFIZ: Signed Bitfield Insert in Zero: an alias of SBFM. </div> <div> SBFM: Signed Bitfield Move. </div> <div> SBFX: Signed Bitfield Extract: an alias of SBFM. </div> <div> SDIV: Signed Divide. </div> <div> SETF8, SETF16: Evaluation of 8 or 16 bit flag values. </div> <div> SETGP, SETGM, SETGE: Memory Set with tag setting. </div> <div> SETGPN, SETGMN, SETGEN: Memory Set with tag setting, non-temporal. </div> <div> SETGPT, SETGMT, SETGET: Memory Set with tag setting, unprivileged. </div> <div> SETGPTN, SETGMTN, SETGETN: Memory Set with tag setting, unprivileged and non-temporal. </div> <div> SETP, SETM, SETE: Memory Set. </div> <div> SETPN, SETMN, SETEN: Memory Set, non-temporal. </div> <div> SETPT, SETMT, SETET: Memory Set, unprivileged. </div> <div> SETPTN, SETMTN, SETETN: Memory Set, unprivileged and non-temporal. </div> <div> SEV: Send Event. </div> <div> SEVL: Send Event Local. </div> <div> SMADDL: Signed Multiply-Add Long. </div> <div> SMC: Secure Monitor Call. </div> <div> SMNEGL: Signed Multiply-Negate Long: an alias of SMSUBL. </div> <div> SMSTART: Enables access to Streaming SVE mode and SME architectural state: an alias of MSR (immediate). </div> <div> Page 9A64 -- Base Instructions (alphabetic order) </div> <div> SMSTOP: Disables access to Streaming SVE mode and SME architectural state: an alias of MSR (immediate). </div> <div> SMSUBL: Signed Multiply-Subtract Long. </div> <div> SMULH: Signed Multiply High. </div> <div> SMULL: Signed Multiply Long: an alias of SMADDL. </div> <div> SSBB: Speculative Store Bypass Barrier: an alias of DSB. </div> <div> ST2G: Store Allocation Tags. </div> <div> ST64B: Single-copy Atomic 64-byte Store without Return. </div> <div> ST64BV: Single-copy Atomic 64-byte Store with Return. </div> <div> ST64BV0: Single-copy Atomic 64-byte EL0 Store with Return. </div> <div> STADD, STADDL: Atomic add on word or doubleword in memory, without return: an alias of LDADD, LDADDA, </div> <div> LDADDAL, LDADDL. </div> <div> STADDB, STADDLB: Atomic add on byte in memory, without return: an alias of LDADDB, LDADDAB, LDADDALB, </div> <div> LDADDLB. </div> <div> STADDH, STADDLH: Atomic add on halfword in memory, without return: an alias of LDADDH, LDADDAH, LDADDALH, </div> <div> LDADDLH. </div> <div> STCLR, STCLRL: Atomic bit clear on word or doubleword in memory, without return: an alias of LDCLR, LDCLRA, </div> <div> LDCLRAL, LDCLRL. </div> <div> STCLRB, STCLRLB: Atomic bit clear on byte in memory, without return: an alias of LDCLRB, LDCLRAB, LDCLRALB, </div> <div> LDCLRLB. </div> <div> STCLRH, STCLRLH: Atomic bit clear on halfword in memory, without return: an alias of LDCLRH, LDCLRAH, </div> <div> LDCLRALH, LDCLRLH. </div> <div> STEOR, STEORL: Atomic exclusive OR on word or doubleword in memory, without return: an alias of LDEOR, </div> <div> LDEORA, LDEORAL, LDEORL. </div> <div> STEORB, STEORLB: Atomic exclusive OR on byte in memory, without return: an alias of LDEORB, LDEORAB, </div> <div> LDEORALB, LDEORLB. </div> <div> STEORH, STEORLH: Atomic exclusive OR on halfword in memory, without return: an alias of LDEORH, LDEORAH, </div> <div> LDEORALH, LDEORLH. </div> <div> STG: Store Allocation Tag. </div> <div> STGM: Store Tag Multiple. </div> <div> STGP: Store Allocation Tag and Pair of registers. </div> <div> STLLR: Store LORelease Register. </div> <div> STLLRB: Store LORelease Register Byte. </div> <div> STLLRH: Store LORelease Register Halfword. </div> <div> STLR: Store-Release Register. </div> <div> STLRB: Store-Release Register Byte. </div> <div> STLRH: Store-Release Register Halfword. </div> <div> STLUR: Store-Release Register (unscaled). </div> <div> STLURB: Store-Release Register Byte (unscaled). </div> <div> STLURH: Store-Release Register Halfword (unscaled). </div> <div> STLXP: Store-Release Exclusive Pair of registers. </div> <div> STLXR: Store-Release Exclusive Register. </div> <div> Page 10A64 -- Base Instructions (alphabetic order) </div> <div> STLXRB: Store-Release Exclusive Register Byte. </div> <div> STLXRH: Store-Release Exclusive Register Halfword. </div> <div> STNP: Store Pair of Registers, with non-temporal hint. </div> <div> STP: Store Pair of Registers. </div> <div> STR (immediate): Store Register (immediate). </div> <div> STR (register): Store Register (register). </div> <div> STRB (immediate): Store Register Byte (immediate). </div> <div> STRB (register): Store Register Byte (register). </div> <div> STRH (immediate): Store Register Halfword (immediate). </div> <div> STRH (register): Store Register Halfword (register). </div> <div> STSET, STSETL: Atomic bit set on word or doubleword in memory, without return: an alias of LDSET, LDSETA, </div> <div> LDSETAL, LDSETL. </div> <div> STSETB, STSETLB: Atomic bit set on byte in memory, without return: an alias of LDSETB, LDSETAB, LDSETALB, </div> <div> LDSETLB. </div> <div> STSETH, STSETLH: Atomic bit set on halfword in memory, without return: an alias of LDSETH, LDSETAH, LDSETALH, </div> <div> LDSETLH. </div> <div> STSMAX, STSMAXL: Atomic signed maximum on word or doubleword in memory, without return: an alias of LDSMAX, </div> <div> LDSMAXA, LDSMAXAL, LDSMAXL. </div> <div> STSMAXB, STSMAXLB: Atomic signed maximum on byte in memory, without return: an alias of LDSMAXB, </div> <div> LDSMAXAB, LDSMAXALB, LDSMAXLB. </div> <div> STSMAXH, STSMAXLH: Atomic signed maximum on halfword in memory, without return: an alias of LDSMAXH, </div> <div> LDSMAXAH, LDSMAXALH, LDSMAXLH. </div> <div> STSMIN, STSMINL: Atomic signed minimum on word or doubleword in memory, without return: an alias of LDSMIN, </div> <div> LDSMINA, LDSMINAL, LDSMINL. </div> <div> STSMINB, STSMINLB: Atomic signed minimum on byte in memory, without return: an alias of LDSMINB, LDSMINAB, </div> <div> LDSMINALB, LDSMINLB. </div> <div> STSMINH, STSMINLH: Atomic signed minimum on halfword in memory, without return: an alias of LDSMINH, </div> <div> LDSMINAH, LDSMINALH, LDSMINLH. </div> <div> STTR: Store Register (unprivileged). </div> <div> STTRB: Store Register Byte (unprivileged). </div> <div> STTRH: Store Register Halfword (unprivileged). </div> <div> STUMAX, STUMAXL: Atomic unsigned maximum on word or doubleword in memory, without return: an alias of </div> <div> LDUMAX, LDUMAXA, LDUMAXAL, LDUMAXL. </div> <div> STUMAXB, STUMAXLB: Atomic unsigned maximum on byte in memory, without return: an alias of LDUMAXB, </div> <div> LDUMAXAB, LDUMAXALB, LDUMAXLB. </div> <div> STUMAXH, STUMAXLH: Atomic unsigned maximum on halfword in memory, without return: an alias of LDUMAXH, </div> <div> LDUMAXAH, LDUMAXALH, LDUMAXLH. </div> <div> STUMIN, STUMINL: Atomic unsigned minimum on word or doubleword in memory, without return: an alias of </div> <div> LDUMIN, LDUMINA, LDUMINAL, LDUMINL. </div> <div> STUMINB, STUMINLB: Atomic unsigned minimum on byte in memory, without return: an alias of LDUMINB, </div> <div> LDUMINAB, LDUMINALB, LDUMINLB. </div> <div> STUMINH, STUMINLH: Atomic unsigned minimum on halfword in memory, without return: an alias of LDUMINH, </div> <div> LDUMINAH, LDUMINALH, LDUMINLH. </div> <div> STUR: Store Register (unscaled). </div> <div> Page 11A64 -- Base Instructions (alphabetic order) </div> <div> STURB: Store Register Byte (unscaled). </div> <div> STURH: Store Register Halfword (unscaled). </div> <div> STXP: Store Exclusive Pair of registers. </div> <div> STXR: Store Exclusive Register. </div> <div> STXRB: Store Exclusive Register Byte. </div> <div> STXRH: Store Exclusive Register Halfword. </div> <div> STZ2G: Store Allocation Tags, Zeroing. </div> <div> STZG: Store Allocation Tag, Zeroing. </div> <div> STZGM: Store Tag and Zero Multiple. </div> <div> SUB (extended register): Subtract (extended register). </div> <div> SUB (immediate): Subtract (immediate). </div> <div> SUB (shifted register): Subtract (shifted register). </div> <div> SUBG: Subtract with Tag. </div> <div> SUBP: Subtract Pointer. </div> <div> SUBPS: Subtract Pointer, setting Flags. </div> <div> SUBS (extended register): Subtract (extended register), setting flags. </div> <div> SUBS (immediate): Subtract (immediate), setting flags. </div> <div> SUBS (shifted register): Subtract (shifted register), setting flags. </div> <div> SVC: Supervisor Call. </div> <div> SWP, SWPA, SWPAL, SWPL: Swap word or doubleword in memory. </div> <div> SWPB, SWPAB, SWPALB, SWPLB: Swap byte in memory. </div> <div> SWPH, SWPAH, SWPALH, SWPLH: Swap halfword in memory. </div> <div> SXTB: Signed Extend Byte: an alias of SBFM. </div> <div> SXTH: Sign Extend Halfword: an alias of SBFM. </div> <div> SXTW: Sign Extend Word: an alias of SBFM. </div> <div> SYS: System instruction. </div> <div> SYSL: System instruction with result. </div> <div> TBNZ: Test bit and Branch if Nonzero. </div> <div> TBZ: Test bit and Branch if Zero. </div> <div> TCANCEL: Cancel current transaction. </div> <div> TCOMMIT: Commit current transaction. </div> <div> TLBI: TLB Invalidate operation: an alias of SYS. </div> <div> TSB CSYNC: Trace Synchronization Barrier. </div> <div> TST (immediate): Test bits (immediate): an alias of ANDS (immediate). </div> <div> TST (shifted register): Test (shifted register): an alias of ANDS (shifted register). </div> <div> TSTART: Start transaction. </div> <div> Page 12A64 -- Base Instructions (alphabetic order) </div> <div> TTEST: Test transaction state. </div> <div> UBFIZ: Unsigned Bitfield Insert in Zero: an alias of UBFM. </div> <div> UBFM: Unsigned Bitfield Move. </div> <div> UBFX: Unsigned Bitfield Extract: an alias of UBFM. </div> <div> UDF: Permanently Undefined. </div> <div> UDIV: Unsigned Divide. </div> <div> UMADDL: Unsigned Multiply-Add Long. </div> <div> UMNEGL: Unsigned Multiply-Negate Long: an alias of UMSUBL. </div> <div> UMSUBL: Unsigned Multiply-Subtract Long. </div> <div> UMULH: Unsigned Multiply High. </div> <div> UMULL: Unsigned Multiply Long: an alias of UMADDL. </div> <div> UXTB: Unsigned Extend Byte: an alias of UBFM. </div> <div> UXTH: Unsigned Extend Halfword: an alias of UBFM. </div> <div> WFE: Wait For Event. </div> <div> WFET: Wait For Event with Timeout. </div> <div> WFI: Wait For Interrupt. </div>

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/157625.html