本例使用PLL产生多个时钟,通过ila观察所产生的各时钟频率是否符合设计;

仿真是理想化的模型,将程序加载到IC中通过ila监测实际状况会更贴切实际应用。

这里使用时钟信号完成ila监测试验,除了“懒”,还有常犯的错——飚车虽然嗨,超速总被拍...

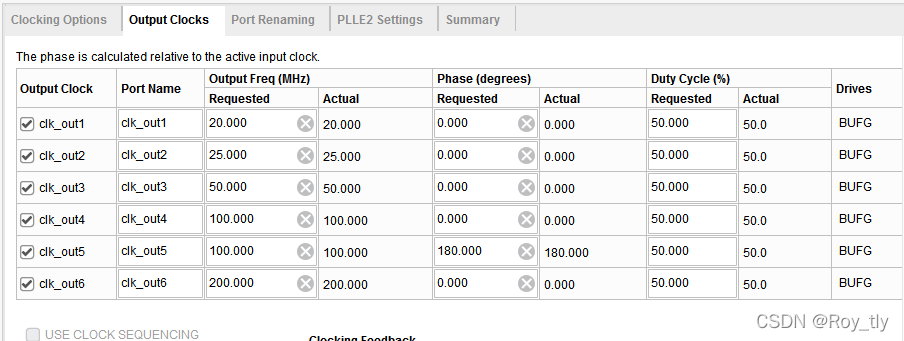

1.设置PLL输出的多时钟

Vivado的官方IP查找操作一致,此处忽略,

通过PLL生成多个不同频率时钟,各时钟概况如下:

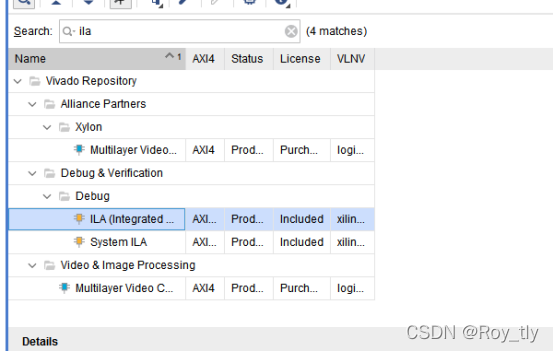

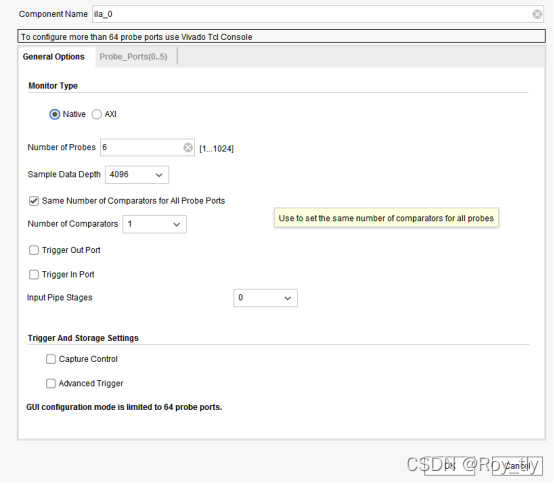

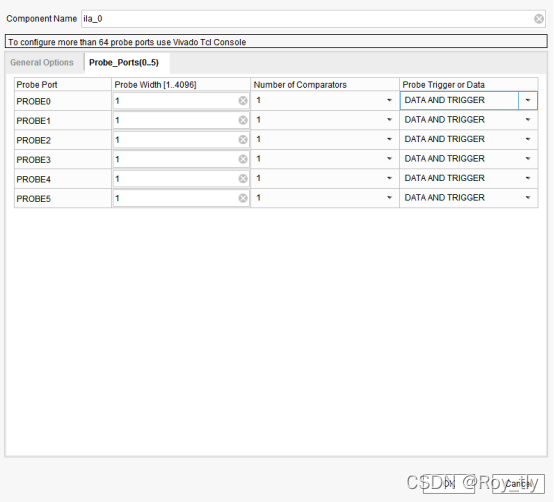

2.ILA配置

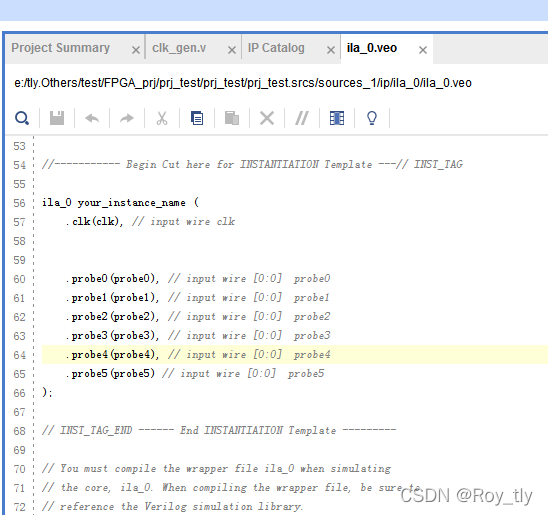

3.ILA接入电路

// // clk_gen.v // module clk_gen ( input sys_clk, input sys_rstn, output clk_20m, //20MHz,50ns output clk_25m, //25MHz,40ns output clk_100m, //100MHz,10ns output clk_100m_p //100MHz,10ns ,反相 ); wire clk_200m, clk_50m, clk_50ns, clk_40ns, clk_20ns, clk_10ns, clk_10ns_p; //时钟生成 clk_wiz_0 inst0 ( // Clock in ports .clk_in1(sys_clk), // input clk_in1 // Control signals .resetn(sys_rstn), // input resetn // Clock out ports .clk_out1(clk_20m), // output clk_out1 .clk_out2(clk_25m), // output clk_out2 .clk_out3(clk_50m), // output clk_out3 .clk_out4(clk_100m), // output clk_out4 .clk_out5(clk_100m_p), // output clk_out5 .clk_out6(clk_200m), // output clk_out6 //这里是摄像头的抓拍速度 // Status signals .locked()); // output locked //ila监测 ila_0 inst1_clk_watch ( .clk(clk_200m), // input wire clk //这里的摄像头反应速度需要足够快===生死线=== //下面的司机,开车的速度不要超过死亡速度 .probe0(sys_rstn), // input wire [0:0] probe0 .probe1(clk_50ns), // input wire [0:0] probe1 .probe2(clk_40ns), // input wire [0:0] probe2 .probe3(clk_20ns), // input wire [0:0] probe3 .probe4(clk_10ns), // input wire [0:0] probe4 .probe5(clk_10ns_p) // input wire [0:0] probe5 ); assign clk_50ns = clk_20m; //对外输出 assign clk_40ns = clk_25m; //对外输出 assign clk_20ns = clk_50m; //内部消化 assign clk_10ns = clk_100m; //对外输出 assign clk_10ns_p = clk_100m_p; //对外输出 endmodule讯享网

4.电路应用

讯享网set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk] set_property -dict {PACKAGE_PIN J15 IOSTANDARD LVCMOS33} [get_ports sys_rstn] set_property -dict {PACKAGE_PIN B19 IOSTANDARD LVCMOS33} [get_ports clk_20m] set_property -dict {PACKAGE_PIN C20 IOSTANDARD LVCMOS33} [get_ports clk_25m] set_property -dict {PACKAGE_PIN P19 IOSTANDARD LVCMOS33} [get_ports clk_100m] set_property -dict {PACKAGE_PIN N18 IOSTANDARD LVCMOS33} [get_ports clk_100m_p]

5.使用方法

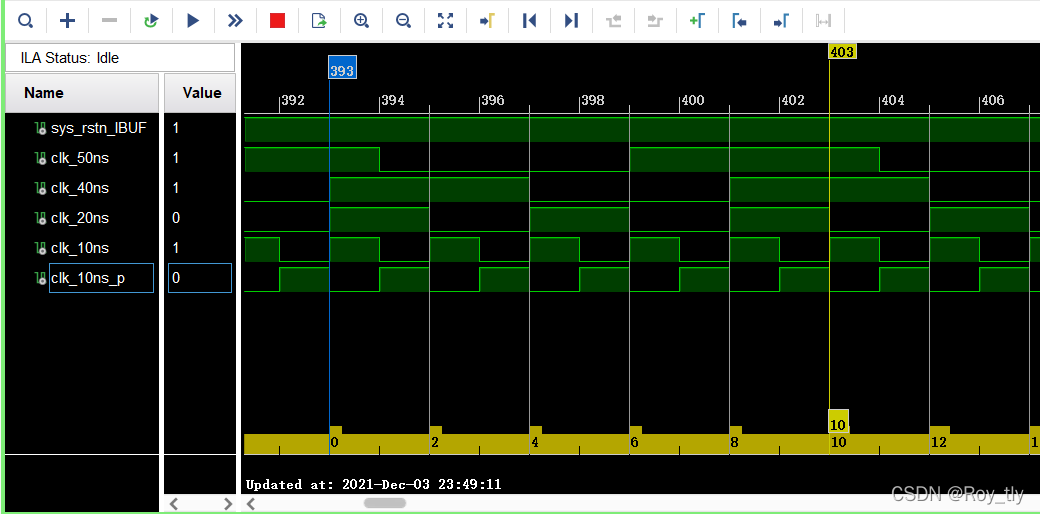

ila采样时钟是200MHz,即每个刻度代表5ns,由以下ila抓取图可得clk_10ns_p和clk_10ns是反相关系,clk_10ns与clk_20ns、clk_40ns、clk_50ns波形周期分别有2倍、4倍、5倍关系,且周期越大,波形变化越快。

综上,该试验没问题。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容,请联系我们,一经查实,本站将立刻删除。

如需转载请保留出处:https://51itzy.com/kjqy/122305.html